проекций принятого сигнала на ортогональные опорные колебания. Этот управляющий сигнал пропорционален синусу удвоенной разности.

## Список использованных источников

- 1. Глазунов, В. А. Цифровые системы передачи информации [Текст]: учебное пособие для вузов/В. А. Глазунов. Самара: Изд-во Самар. гос. аэрокосм. ун-та, 2012. 49с.: ил.

- 2. Системы радиосвязи [Текст]: учебное пособие для вузов / под ред. Н.И. Калашникова. – М.: Радио и связь, 2002. – 352 с.

Глазунов Владислав Александрович, к.т.н., доцент, glazunov\_41@mail.ru Никонов Владислав Алексеевич, магистрант гр. 6131-110401D, rjn-dfcbkbq8719@mail.ru

## УДК 621.3

## СТРУКТУРА КОМПИЛЯТОРА И ПРОШИВКИ ПОД МИКРОКОНТРОЛЛЕРНОЕ FMU ЯДРО НА БАЗЕ FPGA ДЛЯ НАУЧНОЙ КОСМИЧЕСКОЙ АППАРАТУРЫ

Д.П. Григорьев, К.И. Сухачёв «Самарский национальный исследовательский университет имени академика С.П. Королёва», г. Самара

**Ключевые слова:** космический аппарат, компилятор, verilog, микроконтроллер, ПЛИС, RISC.

Для повышения скорости и точности обработки данных в космической научной аппаратуре необходимо применять скоростные вычислительные модули на базе ПЛИС или микроконтроллеров [1, 2]. ПЛИС выгодно использовать для построения логических операций и математических вычислений (DSP), которые выполняются параллельно, не занимая время работы на каждый канал. Однако они сложны с точки зрения построения программного обеспечения, например, операционных систем, или запуска таких интерфейсов, как Ethernet. Микроконтроллеры в свою очередь проще по построению и отладке программного обеспечения и реализации разного рода периферии, но они недостаточны по скорости обработки информации, и практически все имеют только одно вычислительное ядро, ввиду чего невозможно использовать параллельную обработку данных.

Настоящая работа выполнена для разработки нового микроконтроллерного ядра, на базе отечественной ПЛИС, чтобы совместить достоинства как ПЛИС, так и микроконтроллера [3].

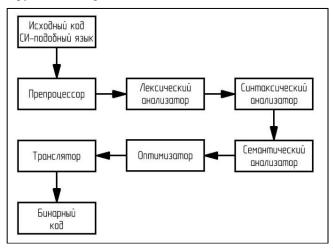

В ходе работы, для вычислительного ядра на базе ПЛИС, была спроектирована структурная схема компилятора, который генерирует двоичный код прошивки по СИ-подобному языку. Компилятор состоит из таких основополагающих частей, как препроцессор, анализатор лексики,

синтаксиса, семантики, оптимизатора и генератора бинарного кода. Препроцессор выполняет роль подготовки исходного кода под дальнейшую обработку компилятором (убирает пробелы и комментарии, подставляет макросы и подключает код из внешних библиотек в единый файл и т.д.). Далее работу начинает лексический анализатор, который составляет таблицу операндов пользователя, состоящую из имени операнда, и его характеристики (тип данных, область видимости и т.д.). После, выполняется синтаксический анализатор, который разбивает весь код на токены (на отдельные операции, символы и т.д.). На этом же этапе происходит разбор приоритетов арифметических операций и разбиение их на отдельные строки кода. Семантический анализатор сверяет семантику, т.е. соответствие типов данных и неявное преобразование типов данных (по необходимости). На стадии оптимизатора устраняются лишние строки кода, которые занимают процессорное время, например, повторное копирование значения из одного регистра в другой. Далее, код имеет вид, который легко транслировать в ассемблерный вид, из которого можно провести генерацию в бинарный код, заменив необходимые команды адресами инструкций, а операнды - данными.

Рисунок 1 – Структурная схема основных этапов работы компилятора

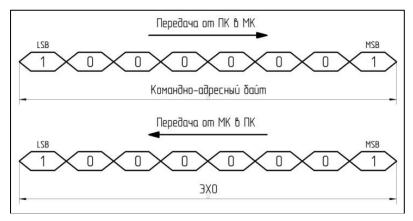

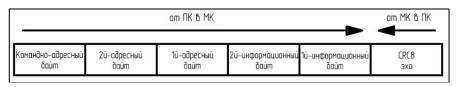

Компилятор на выходе сразу будет формировать пакет для передачи данных. Формат байта и пример пакета для программирования микроконтроллера, показан на рисунках 2 и 3 соответственно. Каждый кадр представляет собой посылку размером 1 байт. Пакет состоит из 5-ти байт - 4 байта передаются из ПК через программатор в МК, и 1 байт отправляется эхом, содержащий контрольную сумму СRС8.

Программирование будет происходить по интерфейсу UART - USB (Virtual Com Port).

Рисунок 2 – Формат программирования микроконтроллера

Рисунок 3 – Формат пакета программирования микроконтроллера

## Список использованных источников

- 1. Воронов К.Е., Григорьев Д.П., Телегин А.М. Исследование алгоритмов для системы контроля поверхности космического аппарата на основе пьезодатчиков // Авиакосмическое приборостроение. 2021.- № 1.- C.40-50.

- 2. Воронов К.Е., Григорьев Д.П., Телегин А.М. Применение нейронной сети прямого распространения для локализации места удара микрочастиц о поверхность космического аппарата // Труды МАИ. -2021. -№ 118. C. 1-35.

- 3. Воронов К.Е., Сухачёв К.И., Воробьёв Д.С. Разработка бортового модуля управления на базе вычислительного IP-ядра //Ракетно-космическое приборостроение и информационные системы. 2021. Т.8. С. 24-38.

Сухачёв Кирилл Игоревич, доцент, с.н.с., kir.sukhachev@gmail.com Григорьев Данил Павлович, инженер-конструктор, аспирант гр. A202, <u>dan-</u>22225@yandex.ru