Министерство высшего и среднего специального образования РСФСР

КУЙБЫШЕВСКИЙ ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ АВИАЦИОННЫЙ ИНСТИТУТ ИМЕНИ С.П. КОРОЛЕВА

Н.Е.Конюхов, Н.И.Филимонов, Е.А.Муштаков

элементы импульсных устройств

Учебное пособие

Утверждено на редакционно-издательском совете института 07.04.76 г.

В пособии рассматривается принцип работы и методы расчета основных элементов импульсных устройств: ключей формирователей импульсов, потенциальных логических схем, триггеров, Основное внимание уделено рассмотрению импульсных элементов, выполненных на биополярных и униполярных транзисторах и интегральных схемах.

Пособие предназначено для студентов, изучающих курсы "Им-пульсные и цифровые устройства" и "Электромагнитная импульсная техника".

#### Глава І. ЭЛЕКТРОННЫЕ КЛЮЧИ

## § І.І. Особенности ключевого режима работы биполярных и униполярных транзисторов

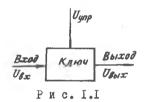

Важнейшими элементами устройств формирования, преобразования и управления импульсами являются ключи (рис. І.І). Основное назначение их состоит в коммутации (замыкании, размыкании) различных

цепей импульсных устройств под воздействием Управляющих сигналов. Ключ в стационарном режиме находится в одном из состояний - замкнутом или разомкнутом. Когда ключ замкнут (включен), сигнал от генератора проходит в нагрузку, когда ключ разоминут (выключен). - не проходит. Часто входные сигналы играют роль управляющих.

Основными требованиями, предъявляемыми к ключам, являются:

- 1) малое внутреннее сопротивление во включенном состоянии и возможно большее в выключенном ( в идеальном ключе внутреннее сопротивление предполагается равным нулю в замкнутом состоянии и бесконечности - в разомкнутом);

- 2) высокое быстродействие, т.е. высокая скорость (малое время) перехода ключа из одного состояния в другое. Такой переход не может быть мгновенным из-за переходных процессов, обусловленных различными паразитными параметрами (емкостями, индуктивностью рассеяния и т.п.):

- 3) высокая стабильность пороговых уровней ключа, т.е. тех уровней управляющего напряжения (или тока), при которых происходит переключение: эти уровни могут изменяться под воздействием температуры, из-за старения элементов, из-за нестабильности источников питания и т.д.

Сравнительный анализ ключевых свойств электронных и полупроводниковых приборов показывает, что последние обладают более высокими ключевыми свойствами. Так, например, электронная лампа способна переключать не более 70% коммутируемого напряжения, в то время как биполярный транзистор - до 95% и выше.

Высокие ключевые свойства полупроводниковых приборов позволили создать импульсные устройства, превосходящие по своим показателям ламповые аналоги. Однако, с другой стороны, перемещение носителей зарядов (электронов и дырок) за счет диффузии и дрейфа в кристаллических решетках германия или кремния полупроводниковых приборов является процессом более инерционным, чем пролет электронов в электронных лампах. Таким образом, если время пролета электронов в лампах обично необходимо принимать во внимание лишь при работе с им пульсами наносекундной длительности, то процессы установления стационарных токов, определяемых статическими характеристиками полупроводниковых приборов, необходимо учитивать при работе с микросекундными импульсами.

## § I.2. Электронные ключи на биполярных транзисторах

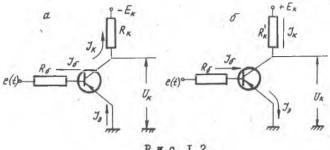

Рассмотрим транзисторные ключевые схемы на биполярных транзисторах ( диффузионных и дрейфовых) типов  $\rho$ -n- $\rho$  и n- $\rho$ -n . В основном рассмотрим схему на дискретных транзисторах типа  $\rho$ -n- $\rho$  . Переход к схемам на транзисторах n- $\rho$ -n сводится лишь к замене полярностей включения источников питания на обратные.

В импульсных устройствах используются все схемы включения транзистора: 09 — общий эмиттер, ОБ — общая база, ОК — общий коллектор, схема "Звезда", когда ни один из выводов электродов транзистора не заземлен, т.е. не является общей точкой, и инверсная схема включения, в которой меняются функциями эмиттер и коллектор транзистора. Наиболее употребительной является схема с 03, поэтому все последующие выкланки относятся к ней.

Принципиальние схеми ключа с 09 на транзисторах разних проводимостей приведени на рис. I.2,a,6; здесь же указани и выбранние положительние направления токов.

Ввелем обозначения:

- $U_{\kappa}$  (иногда  $U_{\kappa\cdot s}$ ) напряжение на коллекторе по отношению к базе;

- $U_{s}$  (иногда  $U_{s,\delta}$ ) напряжение на эмиттере по отношению к базе;

- $U_{\mathcal{S}}$  (иногда  $U_{\mathcal{S},\mathfrak{F}}$ ) напряжение на базе по отношению к эмиттеру;  $U_{\mathcal{S}}=-U_{\mathcal{S}}$  ;

- $U_{\kappa,\partial}$  напряжение на коллекторе по отношению к эмиттеру ( виходное напряжение ключа).

P # C. I.2

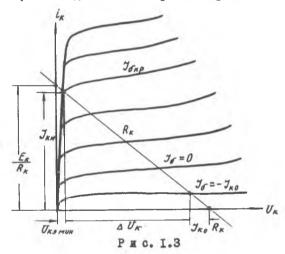

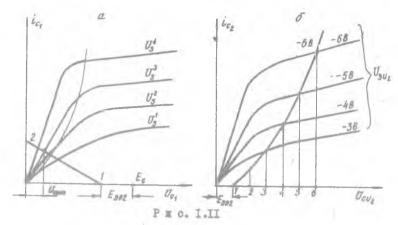

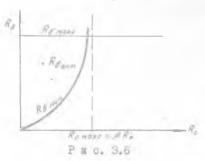

Pacchotphin cemerctbo карактеристик  $i_{\kappa} = f$  ( $U_{\kappa}$ ) и отметим их особенности, важные для кирчевого режима (рис. 1.3).

- Линия критического режимя почти совпадает с осыв токов. Это свидетельствует о том, что напряжение на открытом транзиоторе невелико. (Для германиевых транзисторов при  $\mathcal{I}_{\kappa} < 50$  мА  $\approx 0.2 - 0.3 B$ ).

- 2. Нижняя предельная характеристика не совпадает с осыв напряжений. Это говорит о том, что в закрытом транзисторе протекает ток.

- 3. Густота характеристик увеличивается с увеличением  $J_{\varepsilon}$  на постоянную величину. Это свидетельствует об уменьшении  $\beta$  , т.к.  $\beta$  = ALK В связи с этим будем считать, что  $\beta = \bar{\beta}$ , т.е. 2-828

под  $\beta$  будем понимать среднее значение при изменении  $\mathcal{E}_{\kappa}$  от  $\mathcal{I}_{\kappa}=0$  до  $\mathcal{I}_{\kappa H}$  .

Из характеристик следует, что для насищения транзистора необходимо задать ток  $\mathcal{I}_{\mathcal{S}} > \mathcal{I}_{\mathcal{S}, \times \mathcal{D}} = \frac{J_{\mathcal{SM}}}{\mathcal{S}}$

Как и любой другой, транзисторный ключ можно оценить по следую-

$\Delta U_2$  перепады выходного напряжения и тока. По этим параметрам  $\Delta U_2$  оценивается ключ по мощности;

$\Delta U_{c}$  перепадн входного напряжения и тока. Эти параметры харак-

$R_{four}$  - виходное сопротивление ключа;

$t_{\delta_{KA}}$  и  $t_{\delta_{olkA}}$  — параметри, характеризующие бистродействие ключа. Произведем оценку транзисторного ключа по этем параметрам, воспользоваемись следующим характеристиками ( рис.1.3):

в режиме запирания  $U_2 = U_{\delta b/x} = E_K - J_{K,0} R_K$

в режиме насыщения  $U_2 = U_{\delta blx} = U_{\kappa \cdot \vartheta}$  тип ,

Следовательно,  $\Delta$   $U_{\kappa} = \Delta$   $U_{2} = E_{\kappa} - J_{\kappa,\rho} R_{\kappa} - U_{\kappa,s}$  min .

При  $E_{\kappa} > 10B$ , что практически всегда выполняется, имеем  $U_{\kappa, \sigma, min} \ll E_{\kappa}$  ,  $J_{\kappa, \sigma} R_{\kappa} \ll E_{\kappa}$ , тогда  $\Delta U_2 = \Delta U_{\kappa} \approx E_{\kappa}$

Оцении ключ по параметру 4 62

в режиме запирания  $\mathcal{L}_{\delta_{\delta}/\mathcal{X}} = \mathcal{I}_{\kappa \cdot \sigma}$ ;

в режиме насыщения  $i_{g_{\theta/X}} = \mathcal{I}_K = \mathcal{I}_{K.H} = \frac{E_K - U_{K.9\,min}}{R_K} \approx \frac{E_K}{R_K} = 0$  следовательно,  $\Delta i_2 = \Delta i_K = \frac{E_K - U_{K.9\,min}}{R_K} - \mathcal{I}_{K.9} \approx \frac{E_K}{R_K} = \mathcal{I}_{K.H}$

Из приведенного видно, что по этим двум показателям транзисторный ключ весьма близок к идеальному.

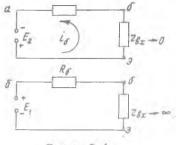

При оценке транзисторного кирча по показателям  $\Delta U$ , и  $\Delta \dot{\ell}_1$  необходимо учесть следующие особенности: так как в режиме насыщения входное сопротивление транзистора очень мало ( $z_{\mathcal{S}_{\mathcal{X}}} = \mathcal{O}$ ), то ток бази определяется величиной источника  $\mathcal{E}_{\mathcal{O}}$  и сопротивлением  $\mathcal{R}_{\mathcal{O}}$ . В этом случае входная цепь транзистора эквивалентна генератору тока (рис.1.4). следовательно,  $\mathcal{J}_{\mathcal{S}} = \frac{\mathcal{E}_{\mathcal{S}}}{\mathcal{E}_{\mathcal{S}}}$ .

При режиме запирания входное сопротивление транзистора велико, так что  $z_{\delta x} \gg R_{\delta}$  и входная цель уподобляется генератору напряжения. Для обеспечения режима запирания условимся выполнять неравенство  $U_{\epsilon x} > 0$  (I.I)

Выходное сопротивление транзисторного ключа принято определять  $(R_{\delta\omega x} = R_{\kappa})$  как наихудший случай.

Прежде чем оценивать транзисторный ключ по быстродействию, необчодимо более подробно рассмотреть режими запирания и наснаения. Это необходимо сделать. так как в закрытом транзисторе, как уже отмечалось выше. протекают токи, оказывающие в ряде случаев большое влияние на работу некоторых cxem.

Режим запирания

Ввелем следующие обозначе-HEEL!

P # C. I.4

$\mathcal{I}_{\kappa,\rho}$  — обратный ток коллекторного перехода, замеренный при разом кнутой цепи эмиттера:

$\mathcal{I}_{a,b}$  — обратний ток эмиттерного перехода, замеренный при разомкнутой пени коллектора.

У реальных транзисторов наследается довольно сильная зависимость этих токов от величины запирающего напряжения, поэтому введем обозначения начальных значений обратных токов изолированных переходов для малых значений  $U_{300}$  0.1 - 0.2 В:

у - начальное значение обратного тока коллекторного перехода;

— начальное значение обратного тока эмиттерного перехода.

Токи, протекажние в транзисторе в режиме запирания ( не изолированные переходы), будем обозначать:

$\mathcal{J}_{(\kappa,\sigma)}$  — обратний ток коммекторного перехода транзистора;

до) - обратный ток эмиттерного перехода транзистора;

$\mathcal{J}_{(\vec{r}\cdot\vec{o})}$  — обратный базовый ток транзистора;

$\mathcal{J}'_{(\kappa,o)}$  ,  $\mathcal{J}'_{(\beta,o)}$  —  $\mathcal{J}'_{(\beta,o)}$  — начальные значения обратных токов тран-SECTODA.

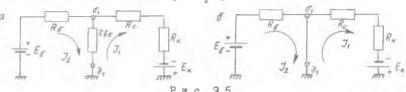

Токи  $\mathcal{I}_{(\mathscr{I},0)}$  в  $\mathcal{I}_{(\mathscr{K},0)}$  часто назнвают обратными одновременными токами, т.е. оба перехода работают одновременно. Направления этих токов показаны на рис. І.5. Очевидно, что  $J_{(5.0)} = J_{(\kappa \cdot 0)} + J_{(9 \cdot 0)}$ . Влия-

ние токов  $\mathcal{I}_{(\kappa,o)}$  и  $\mathcal{I}_{(\beta,o)}$  на работу транзистора невелико, так как эти тепловне составляющие даже при высоких температурах на один - два порядка меньше рабочех токов. А вот ток  $\mathcal{I}_{(E,0)}$  оказывает заметное влияние на работу транзисторного ключа.

Из кврестных уравнений Эберса - Молла 3 можно получить выражение

P.m. c.I.5

$$J'_{50} = J'_{(3.0)} + J'_{(\kappa.0)} = J'_{\kappa.0} \frac{\alpha - \alpha_i (2\alpha - 1)}{\alpha (1 - \alpha \alpha_i)}, \qquad (I.2)$$

« с - коэффициент передачи тока эмиттера при инверсном вклю-TEHNA.

Так как  $\propto -1$  то из выражения (1.2) следует, что  $\mathcal{J}_{\delta,0}' - \mathcal{J}_{\kappa,o}$  , т.е.  $\mathcal{I}_{(\partial,\rho)} \longrightarrow \mathcal{O}$  , т.е. в реальных транзисторах можно не учитывать тепловую составляющую эмиттерного перехода, а считать

$$\mathcal{I}_{\sigma,\varrho} = \mathcal{I}_{\kappa,\varrho} \ . \tag{I.3}$$

Все тепловые составляющие, как это следует из уравнений Эберса-Молла, зависят от величины запирающего напряжения и окружающей температури. Чтобы учесть это обстоятельство, примем в дальнейшем

$$J_{s,o} = J_{\kappa,o} + 1.5 \frac{E_{\kappa}}{Z_{\kappa}} / n\rho u \quad t^* \mathcal{C} = t^* \mathcal{C} \, max = J_{\omega.\delta}, \tag{1.4}$$

т.е. это экстремальное значение тепловой составляющей, взятое при  $U_{3an} = I, 5 \, \mathcal{E}_{\kappa}$  и максимальной температуре.

Тогда условия запирания транзистора сведутся к следующему условию: так как в любом случае базовую цепь транзистора можно привести к виду, показанному на рис. І.6, то  $U_{\varepsilon,j} > 0$  — режим запирания.  $U_{\varepsilon,j} =$

P M C. I.6

$=E_{\partial A}\delta$   $\mathcal{J}_{A}$  O  $R_{\delta \cdot \partial A}\delta$  > O или  $R_{\delta \cdot \partial A}\delta$  <  $\frac{E_{\partial A}\delta}{\mathcal{J}_{A}\delta}$  . Подставляя сида вместо  $\mathcal{J}_{K,O}$  его экстремальное значение, получим условие запирания транзистора, рассчитанное на наихудший случай

$$R_{6.3\kappa\delta} < \frac{E_{3\kappa\delta}}{J_{M\delta}} . \tag{I.5}$$

Режим насыщения

Как следует из характеристик (рис. І. 3)

условие насыщения транзистора записывается следующим образом:

$$\mathcal{I}_{\sigma} \geqslant \mathcal{I}_{\sigma,\kappa,\rho} = \frac{\mathcal{I}_{\kappa,\mu}}{2} = \frac{\mathcal{E}_{\kappa}}{2} . \tag{I.6}$$

$\mathcal{J}_{\sigma} \geqslant \mathcal{J}_{\sigma,\kappa,\rho} = \frac{\mathcal{J}_{\kappa,\kappa,\rho}}{\beta} = \frac{\mathcal{E}_{\kappa}}{\mathcal{R}_{\kappa,\beta}}$ . (I.6) При задании в базу тока  $\mathcal{J}_{\sigma} > \mathcal{J}_{\sigma,\kappa,\rho}$  ток коллектора уже не изменяется, так как транзистор " стянулся в точку", и  $\mathcal{J}_{\kappa,\kappa}$  не зависит от транзи стора: JKH = EK

В этом случае в базе накапливается избиточний заряд, вносимий дирками. Чтобы охарактеризовать это состояние транзистира. вводится коэффициент - степень насыщения или глубина насыщения:

$$\mathcal{N}=rac{J_6}{J_{5..Kp}}$$

или  $\mathcal{N}=rac{J_6-J_{5.Kp}}{J_{5..Kp}}$ . (I.7) Как видно, режим насыщения определяется не величинами токов, а их

соотношением и может иметь место при весьма малых токах.

С увеличением степени насыщения напряжения между электродами транзистора все меньше и меньше зависят от токов, поэтому насыщенный ключ более стабилен.

Переходене характеристики транзисторного ключа

Вопросн бистродействия кирча, т.е. время его перехода из одного состояния в другое, наиболее важные в транзисторной технике, так как именно они и определяют бистродействие триггерных скем, мультивибраторов и т.п.

Анализ переходных характеристик ключа с 09 удобно провести, используя положение заряда [3], связивающего его в базе транзистора с токами. Эта связь выражается зависимостью

$$\frac{dQ}{dt} + \frac{Q}{V} = \mathcal{I}_{f} . \tag{I.8}$$

$$Q - заряд в базе;$$

т - среднее время жизни носителей в базе ( в ряде источников применяется обозначение  $\tau_{s}$  ).

В стационарном режиме имеем

$$Q = \tau \, \mathcal{I}_{\mathcal{E}} \, \cdot \tag{I.9}$$

На границе насищения, когда  $\mathcal{I}_{\sigma} = \mathcal{I}_{\sigma,\kappa\rho}$  можно записать

$$J_{\sigma \cdot \kappa \rho} \ \tau = \mathcal{Q}_{\partial \rho} \tag{I.10}$$

или в другой форме

$$\mathcal{Q}_{\mathcal{E}\rho} = \mathcal{T} J_{\kappa,\rho} = \mathcal{T} \frac{J_{\kappa,H}}{\beta} \approx \mathcal{T}_{\alpha} J_{\kappa,H}$$

, (I.II) где  $\mathcal{T}_{\alpha}$  — среднее время пролета носителей через базу.

Выразив токи в выражения (1.7) через заряды, мы получим наглялную интерпретацию степени насыщения:

$$N = \frac{Q}{Q_{RP}} \quad \text{MOH} \quad N = \frac{Q - Q_{RP}}{Q_{RP}} \quad (I.I2)$$

В литературе встречентся сбе форми записи степени насыщения. Численная разность между ними равна единице. Условимся в пальнейшем применять запись

$$N = \frac{Q - Q_{2P}}{Q_{2P}} = \frac{J_5 - J_{5NP}}{J_{5NP}}$$

(I.13)

В операторной форме выражение (1.8) можно записать как

$$Q_{(\rho)} = \frac{J_{\sigma(\rho)} \tau - \tau_{(\rho)} Q_{(\rho)}}{I + \rho \tau} . \tag{I.14}$$

В частном случае, когда Q(0) = 0, получим

$$Q_{(\rho)} = \frac{J_{\kappa}(\rho) \, \mathcal{T}}{J_{+} \, \rho \, \mathcal{T}} = \frac{J_{\delta}(\rho)}{\rho + \frac{J_{\delta}}{2}} \, . \tag{I.15}$$

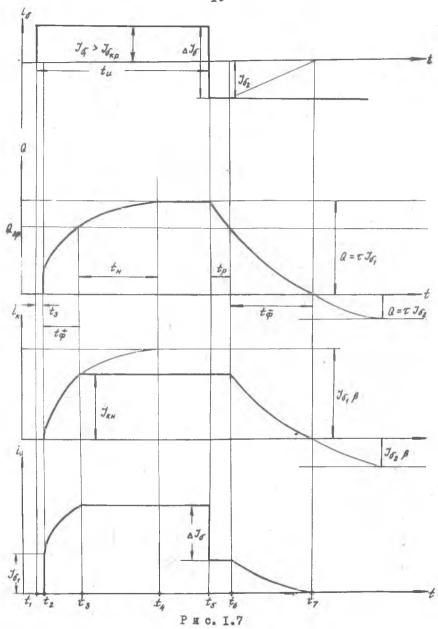

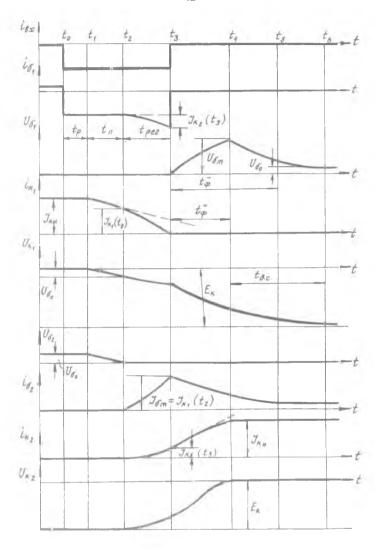

$Q_{(\rho)} = \frac{J_{\kappa}(\rho)}{I + \rho \, \mathcal{T}} - \frac{J_{\kappa}(\rho)}{\rho + J_{\kappa}}$ . Процесс замикания киюча состоят из трех стадий ( рис.І.?): задержки виличения  $-t_{3}$  :

формирования положительного фронта  $-t_{\phi}^{\tau}$  :

3-828

накопления носителей (заряда) в базе  $-t_H$  ; Процесс размыкания ключа состоит из следующих стадий: рассасивания избиточного заряда в базе  $-t_p$  ; формирования отрицательного фронта - 🛵 .

Стадия запержки (  $t_2 - t_1 = t_3$  )

Эта стация обусловлена перезарядкой барьерных емкостей  $\mathcal{C}_{x}$  $\mathcal{C}_{\kappa}$  под воздействием входного сигнала. Так как эта стадия лишь сдвигает переходные характеристики и является наименее продолжительной из всех стадий ( порядка десятков наносекунд), то учет ее обычно проводится в редких случаях.

Стадия формирования  $t_{\varphi}$  ( $t_3$ - $t_2$ = $t_{\varphi}$ )

Tar kak upu  $t < t_2$  Q = 0 воспользуемся выражением (I.I5), учитываюцим это обстоятельство. Подставим в (I.I5) значение тока  $\mathcal{I}_{s_1}$ : Переходя к оригиналу, получим  $Q(t) = \mathcal{I}_{s_1} \tau \left(1 - e^{-\frac{t}{\tau}}\right)$ При достижении  $Q_{(t)}=Q_{z_R}$  закончится формирование  $t_{\varphi}^+$  , следовательно,  $Q_{2p} = J_{81} \tau \left(1 - e^{-\frac{\tau_p}{\tau}}\right)$ .

Подставляя сюда значение  $\,arrho_{2

ho}\,\,$  из (I.II), определим значение  $\,t_{arphi}^{\, au}$  :

$$t_{\varphi}^{+} = \tau \ln \frac{J_{\delta I}}{J_{\delta I} - \frac{J_{\delta I}}{B}} \tag{I.16}$$

$t_{\varphi}^{+} = \tau \ln \frac{J_{g_{1}}}{J_{g_{1}} - J_{g_{2}}} \tag{I.16}$  Так как  $Q = \frac{\tau}{\beta} \mathcal{I}_{\kappa}$ , можем получить  $L_{\kappa}(t) = \beta \mathcal{I}_{g_{1}}(1 - e^{\frac{t}{c}}), \tag{I.17}$  т.е. ток коллектора нарастает по экспоненциальному закону. При услоени сильного видечавитего сигнала, когда  $\beta J_{s_1} \gg J_{s_M}$  , фронт импульса близок к линейному. Раздагая в ряд экспоненту (І.17) или догарифм (1.16), получим для сильного сигнала

$$\dot{t}_{\varphi}^{+} \approx \tau_{\alpha} \frac{J_{\kappa, \eta}}{J_{s, t}} \quad \nu \quad \dot{\iota}_{\kappa} (t) = \frac{\beta}{\tau} J_{s, t} t . \tag{I.18}$$

Стадия накогления  $t_H$   $(t_H - t_3 = t_H)$ .

С момента  $t_{\varphi} = t_3$  все три тока (  $\mathcal{I}_{g_1}$  ,  $\mathcal{I}_{\kappa}$  ,  $\mathcal{I}_{g}$  ) не изменяются. Продолжается лишь накопление заряда в базе. Этот процесс закончится через время £ = 3 T .. .

т, - время ( среднее ) жизни носителей в базе в режиме накопленин.  $\tau_{n} < \tau$ , так как увеличивающееся количество дирок в базе увеличивает вероятность встречи дирки и электрона, т.е. увеличивает скорость рекомбинации. Следовательно, время жизни носителей уменьмается. Обично полагают, что  $T_{\mu} \approx 0.8 \, \tau$

Виражение (1.19) справедииво, если длительность видочающей ступень-RH  $\mathcal{I}_{s_I}$  , t.e.  $t_{\mu}\gg au_{_H}$  . В противном случае необходимо пользоваться выражением

$Q(tu) = \mathcal{I}_{51} \, \mathcal{I}_H \, \left(1 - e^{-\frac{tu}{\tau_H}}\right).$ (1.20)

Стация рассасивания  $t_{P}$  (  $t_{G}$  -  $t_{S}$  =  $t_{D}$  )

В момент времени  $t_{\rm S}$  на базу транзистора подается виключаюций ток  $J_{\sigma s}$  , т.е. ток обратного направления. Очевилно, что пока не исчезнет ( рассасется) избыточный заряд в базе, транзистор не выйдет из режима насыщения. Следовательно, ток комлектора  $\ell_{\kappa}$  ( t ) на этой стадии остается постоянным. Эта задержка в выключении. специфическое свойство транзисторов, называется временем рассасыванин избиточного заряда в базе.

Для анализа этой стаден необходимо воспользоваться выражением (I.14), TER RER B STOM CAYRE  $Q(0) \neq 0$ .

B comem chydae mmeem:  $\mathcal{Q}(0) = \mathcal{Q}(tu) = \mathcal{I}_{s_1} \mathcal{I}_{H} \left(1 - e^{-\frac{t_u}{t_{s_1}}}\right)$ . Подставляя все это в (I.I4) получий  $\mathcal{Q}(\rho) = \frac{\mathcal{I}_{s_1} \mathcal{I}_{H}}{\rho}$ MIH.

переходя к оригиналу,  $Q(t) = Q(0) e^{\frac{t}{t_{+}}} \mathcal{J}_{52} \tau \left(1 - e^{\frac{t}{t_{-}}}\right)$  Отсида при  $t = t_{p}$   $Q(t) = Q_{2p}$  , следовательно,  $t_{p} = \tau \ln \frac{Q(0) - \mathcal{J}_{52} \tau}{Q_{2p} - \mathcal{J}_{52} \tau}$

(I.2I)

(I.22)

и замена  $\tau$  на  $\tau_{H}$  . Обично полагают  $\tau_{p} = (0.8-0.9)\,\tau_{H} = (0.7 \div 0.8)\,\tau$ При наличии сильного выключающего сегнала можно получеть

$$t_{p} = \frac{\tau_{p}}{R} \frac{NJ_{NH}}{\Delta J_{6}} \quad \text{usin } t_{p} = \tau_{p} \frac{J_{61}}{\Delta J_{c}}, \qquad (I.23)$$

Стадии формирования  $t_{\phi}$  (  $t_7$  -  $t_6$  =  $t_{\phi}$  )

Эта стадия является продолжением предыдущей, следова-Teabro, bochoalsobarmech temm we homemam, mozem howyteth ho anamourm  $Q(t) = Q(0) e^{-\frac{t}{t}} + J_{s2} \tau \left(1 - e^{-\frac{t}{t}}\right)$ . B stom chydae  $Q(0) = Q_{ep}$

При

$$t=t_{\varphi}^-$$

имеем  $\mathcal{Q}(t)=\mathcal{Q}$  , подставляя все это в (I.I4) получаем:

$$\mathcal{Q}=\tau\frac{J_{KN}}{\beta}\,e^{-\frac{t_{\varphi}}{\xi}}+J_{\mathcal{S}_2}\,\tau\,\left(1-e^{-\frac{t_{\varphi}}{\xi}}\right)$$

или отседа

$$t_{\varphi}^-=\tau\ln\frac{J_{KN}-J_{\mathcal{S}_2}}{J_{\mathcal{S}_2}}\,.$$

$$t_{cp} = \tau \ln \frac{\frac{1}{8} J_{52}}{J_{52}}$$

(I.24)

(I.24)

$\iota_{\varphi} = \tau \ln \frac{J_{s_2}}{J_{s_2}}$  (I.24) При наличии сильного выключающего сигнала, т.е. когда  $\left/J_{s_2}\right/\gg \frac{J_{\kappa N}}{\beta}$ , солучим  $t_{\overline{\varphi}} \approx \frac{\tau}{\beta} \frac{\mathcal{I}_{AH}}{\mathcal{I}_{-}} \; .$ MNPVIOL (1.25)

На рис. 1.7 приведены законы изменения токов транзистора в режиме переключения. Следует отметить. что выражение (1.25) дает несколько заниженный результат, так как в нем не учтено уменьшение базового тока  $J_{\rm f,2}$  на этой стадии из-за увеличивающегося входного сопротивления транзистора.

## § 1.3. Электрические ключи на полевых транзисторах

Полевне транзисторы с изолированным затвором (МДП-транзисторы) сбладают рядом достоинств, благодаря которым они имеют перспективы широкого применения. К этим достоинствам прежде всего относится их более высокая по сравнению с биподярными транзисторами технологичность и возможность изготовления большого числа приборов (несколько сотен) на одной подложке. Поэтому наиболее целесообразно применять полевне транзисторы в интегральных схемах. Другое важное их достоинство состоит в том, что управление током в выходной цени осуществинется изменением поперечного электрического поля в канале, т.е.изменением напряжения на затворе, изолированном от канала слоем диэлектрика. Благодаря этому МДП-транзисторы имеют очень высокое входное сопротивление и в статическом состоянии практически не потребляют энергии во входной цепи.

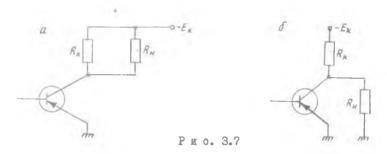

Ключи на МЛП-гранзисторах строятся по той же скеме (рис.І.І). нагрузкой может служить, как и в ключах на биполярных гранзисторах. резистор. При интегральном исполнении, которое для МПП-транзисторов следует считать основным, в качестве нагрузки обычно применяют также МДП-транзистор. В этом случае ключ состоит из двух транзисторов: коммутирующего и нагрузочного. С точки зрения интегральной технологии, более целесообразным оказывается создание в качестве нагрузки второго транзистора, чем линейного резистора с достаточно большим номиналом.

Нагрузочний транзистор может онть с встроенным и липупированным 4-828

каналами, с каналом  $\rho$  — типа и  $\rho$  — типа, его затвор может бить соединен со стоком, с истоком, иметь отдельний источник питания и т.д. В зависимости от этого нагрузка может иметь большое число видов вольт—амперных характеристик, причем каждая из них удобна для какого—либо конкретного применения ключа. Таким образом, помимо технологической целесообразности, двухтранзисторная схема обладает универсальностью, обеспечивающей в принципе получение наилучших свойств ключа в каждом конкретном случае (быстродействие, энергетическую экономичность и т.д.).

## Ключ с линейной нагрузкой

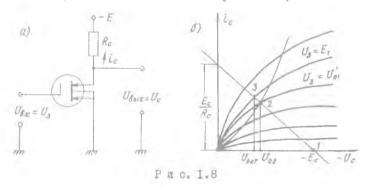

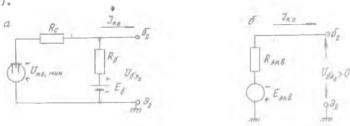

На рис.1.8,а представлена схема ключа на транзисторе с индупированным каналом  $\rho$  — типа с резистором в качестве нагрузки.

В зависимости от уровня входного напряжения  $U_{\delta x}$  транзистор может быть либо в открытом, либо в закрытом состоянии. При этом выходное напряжение  $U_{\delta b/x}$ , равное напряжению на стоке  $U_{c}$ , будет соответственно, либо малым по абсолютному значению, либо большим.

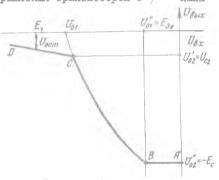

Имеются, однако, и существенные особенности в работе ключа на МДП-транзисторе. Для их выяснения обратимся к рис. I.8, б на котором изображено семейство выходных характеристик транзистора  $\ell_c = f(\mathcal{O}_c)$  для разных напряжений на затворе  $\mathcal{O}_g$  и проведена нагрузочная линия, соответствующая данному значению сопротивления резистора  $\mathcal{R}_c$ . Существуют две области характеристик: пологая ( " пентодная") область, соответствующая большому внутреннему сопротивлению транзистора и слабой зависимости  $\ell_c$  от напряжения  $\mathcal{O}_c$ , и крутая ( "триодная"), где характеристики представляют собой нучок почти прямых линий, проходящах через начало координат. Линия раздела между обеими областями

показана на рис.1.8,6 пунктиром и соответствует значениям напряжения на стоке:

$U_c = U_s - E_{s,a}$ (1.26)

где  $\mathcal{E}_{3,q}$  - напряжение запирания транзистора, т.е. такое напряжение на затворе, при котором транзистор либо отпирается, и в нем появляется ток стока, либо запирается, если напряжение  $U_3$  изменяется в другом направлении.

Следует отметить, что крутая область представляется в виде сравнительно широкого пучка характеристик. В обычном масштабе они не вырождаются в линию, как в маломощных биполярных транзисторах. Поэтому этот ключ не имеет четко определенного уровня выходного напряжения после вкирчения, так как остаточное напряжение на стоке откритого транзистора в крутой области зависит, вообще говоря, от напряжения на затворе. Важно так же и то, что напряжение запирания  $\mathcal{E}_{i,j}$ довольно велико, порядка единиц вольт.

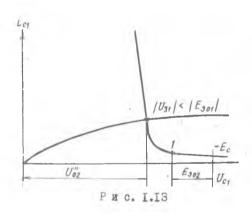

Работа илича илирстрируется его статической характеристикой  $U_{\delta yx}=f\left(U_{\delta x}

ight),$  представленной на рис.І.9. Для управлення транзистором с ho - кана-

иом напряжение  $U_{\delta x}$  полжно быть отрацательным. При  $/U_{\delta x}/<$  $</E_{3,0}/$  (участок AB) транзистор закрыт.

Ток стока равен тепловому току  $\mathcal{I}_{c,o}$  , т.е. очень мал (значительно меньше теплового тока  $\mathcal{I}_{\kappa,\sigma}$  в биполярных транзисторах). Пренебрегая падением напряжения на резисторе  $R_c$  sa cuer eroro roka, mozeo считать, что выходное напря-

P # C. I.9

жение  $U_{four}$  равно напряжению питания  $\mathcal{E}_{\mathcal{C}}$  , т.е.  $U_{g2}'' = -\mathcal{E}_{\mathcal{C}}$  .

Когда напряжение  $U_{\delta r}$  , увеличиваясь по абсолютному значению, достигает уровня  $U_{o_1}'' = E_{g_{o_2}}$ , транзистор откривается ( точка I на рис. I.8,6), и при дальнейшем увеличении напряжения / $U_{\ell,x}$ / ток стока  $i_c$ нарастает, а напряжение  $/U_{\delta o x}/$  уменьшается ( участок ВС). Это изменение  $U_{\ell_{h/x}}$  нелинейно, так как нелинейна зависимость  $\ell_{c} = f\left(U_{3}\right)$  в пологой области карактеристик. Уровнем включения ключа можно считать границу между пологой и крутой областями характеристик. На основании (1.26) с учетом того, что в данном случае  $U_{\ell_X} = U_3$  и  $U_{\ell_{D/X}} = U_m$ можем записать  $U_{\alpha 1} = U_{\alpha 2} + E_{\alpha \alpha}$ ,

где  $U_{c2}$  — напряжение на стоке, соответствующее точке пересечения линии нагрузки с границей областей характеристик (точка 2 на рис. 1.8,6).

Соответствующий этому уровень выходного напряжения  $U_{0z}^1 = U_{0z}^2 = U_{0z}$  При дальнейшем изменении  $U_{\delta x}$  ( участок СД) напряжение  $U_{\delta \nu/x}$  тоже изменяется, но не так резко, как в пологой области характеристик. Если при работе ключа напряжение  $U_{\delta x}$  достигает определенного уровня  $\mathcal{E}_{\tau}$ , то на выходе будет соответствующее ему остаточное напряжение  $U_{ocm}$  ( точка 3 на рис. 1.8,6).

Заметим, что сопротивление транзистора в крутой области характеристик мало (обично сотни ом). Поэтому, выбирая сопротивление резистора  $\mathcal{P}_{\mathcal{C}}$  сравнительно большим, можно получить достаточно малое остаточное напряжение  $U_{\mathcal{OCM}}$ , и его изменение при изменении входного напряжения  $U_{\mathcal{H}_{\mathcal{X}}}$  будет также незначительно по сравнению с величиной  $\mathcal{E}_{\mathcal{C}}$ .

Ключ на транзисторах с каналами одного типа проводимости

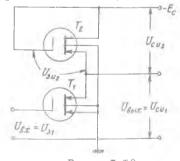

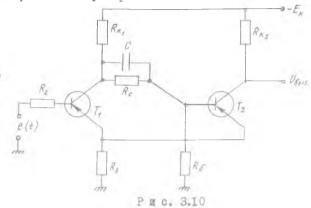

На рис.І.ІО приведена схема ключа на двух транзисторах с индуцированным каналом  $\rho$  — типа. Коммутирующий транзистор  $\mathcal{T}_{r}$  управля—

P M C. I.IO

ипа. Коммутирующий транзистор  $\Gamma_{\tau}$  управля—

о- $E_{c}$  ется входным напряжением  $U_{\delta,x}$ , подаваемым на затвор. Затвор нагрузоч—

ного транзистора  $\Gamma_{2}$  соединен с его

стоком. В процессе работы ключа напряжение  $U_{3U_{2}}$  между затвором и истоком этого транзистора изменяется в

соответствии с изменением выходного

напряжения  $U_{\delta,o,x}$ , так как

$U_{3U_2} = -E_C - U_{8s/x}$ . (1.27) Этот ключ отличается от ключа с линейной нагрузкой (рис.1.8,а) только

характером нагрузки. На рис.І.ІІ, а изображено семейство выходных характеристик  $i_{c_f} = f\left(U_{c_f}\right)$  коммутирующего транзистора  $\mathcal{T}_f$  при  $U_3 = const$ . Там же показана нагрузочная кривая, представляющая собой вольт—амперную характеристику нагрузочного транзистора  $\mathcal{T}_2$ , изображенную в тех же координатах.

Построение характеристики транзистора  $\mathcal{T}_{\mathcal{L}}$  при  $U_{\mathcal{L}\mathcal{U}} = U_{\mathcal{J}\mathcal{U}}$ , т.е.

при соединении затвора со стоком, иллострируется примером на рис. I.II,6 (масштаб по оси ординат сильно увеличен). Для каждого значения  $U_{3U_2}$  на характеристике находится точка, соответствующая равенству  $U_{3U}=U_{CU}$ . Приведенная через эти точки кривая и есть искомая характеристика нагрузочного транзистора в этом режиме.

Так как в пологой области ток стока  $\mathcal{U}_c$  почти не зависит от напримения на стоке  $\mathcal{U}_{\mathcal{CU}}$  , то эта характеристика выражает зависимость тока стока от напримения на затворе  $\mathcal{U}_{\mathcal{SU}}$  , т.е. по существу явияется проходной характеристикой транзистора  $\mathcal{T}_{\mathcal{D}}$  .

Так как полученная характеристика в отличии от характеристики резистора не проходит через начало координат, то и нагрузочная кривая на рис. I.II, а начинается не от точки  $U_{c_I} = -E_c$ , а девее на величину  $E_{302}/$  .

Вольт-ампериая характеристика транзистора  $\frac{7}{2}$  существенно нелинейна, поэтому этот кимч принято называть кимчом с нелинейной нагрузкой.

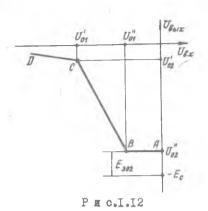

Для получения достаточно маного остаточного напряжения на выходе при открытом коммутирующем транзисторе необходимо, чтоби нагружения кривия на рис.I.II, а проходила достаточно полого, т.е. проходила характеристика транзистора имела достаточно маную крутизму С этой целью его канал делается более узким, чем у транзистора  $\mathcal{T}_{f}$ . Характеристика передачи ключа  $\mathcal{U}_{f,t,x} = f(\mathcal{U}_{f,x})$ ноказана на рис.I.I2. Она отличается от аналогичной характеристики для ключа с линейкой нагрузкой тем, что уровень выходного напряжения  $\mathcal{U}_{02}^{-}$  при выключением ключе здесь не равен  $-\mathcal{E}_{0}$ . Кроме того, характеристика проходит яваче на 3-828

участке ВС. Выясним причины этих отличий, из которых наиболее важным является первое. При  $/U_{\delta x}/<$   $</E_{301}/$  коммутирующий транзистор  $I_{7}$  закрыт. Нагрузочный же транзистор  $I_{2}$  при этом находится на грани запирания, т.е. он открыт настолько, насколько это требуется для пропускания через него малых токов закрытого транзистора  $I_{7}$ : теплового тока  $I_{C01}$  и тока утечки, а также тока нагрузки, если она подключена к выходу.

Для пояснения этого обратимся

к рис.І.13. На нем изображена выходная характеристика  $i_{c1} = f\left(U_{c1}\right)$  закрытого транзистора  $I_{7}$  (для  $\left|U_{31}\right| < \left|E_{301}\right|$ ) и нагрузочная линия, представляющая собой " обращенную " проходную характеристику тран—

зистора 72 . Отличие этого рисунка от рис.І.ІІ, а состойт в том, что масштаби

по оси ординат сильно увеличены, чтобы были видны характеристики закрытых транзисторов (на рис.І.ІІ, а они

совпадают с осью ординат)

Благодаря тому, что транзистор  $\mathcal{T}_2$ , как уже отмеча-лось, имеет более узкий канал, его тепловой ток  $\mathcal{T}_{co2}$  и ток утечки меньше, чем у транзистора  $\mathcal{T}_{\ell}$ . Поэтому

точка I, соответствующая границе запирания транзистора  $\mathcal{T}_2$ , лежит ниже характеристи: транзистора  $\mathcal{T}_f$ . Точка пересечения характеристик, которая определяет ток, протекающий через транзисторы, получается левее точки I ( транзистор  $\mathcal{T}_2$  открыт), но волизи нее. При этом напряжение между стоком и истоком транзистора  $\mathcal{T}_2$  практически равно напряжению запирания  $\mathcal{L}_{302}$ , и уровень выходного напряжения  $\mathcal{U}_{60/2}$  на учетстве AB характеристики передачи олизок к величине

$$U_{02}^{"} = E_{E} + /E_{302}/. {(1.28)}$$

После отпирания транзистора  $\mathcal{T}_{i}$  (точка B) оба транзистора работают в пологой области карактеристик. Этим обусловлено линейное изменение  $U_{f_{\theta}/x}$  на участке ВС. В точке С транзистор  $\mathcal{T}_{t}$  переходит в крутую область характеристик. Если напряжение  $U_{\theta x}$  достигает, например, уровня  $U_{\delta x} = U_3^3$ , остаточное напряжение  $U_{ocm}$  будет соответствовать точке 2 на рис. I.II, а.

В приведенных выше рассуждениях предполагалось, что напряжения запирания обожк транзисторов при переключении остаются постоянными. Это справедливо, когда истоки транзисторов соединени с подложкой. В интегральных схемах обично общая подложка " заземлена", как это показано на рис. I.IO, и с нер соединен лишь исток транзистора  $T_{r}$  . Поэтому при возрастании выходного напряжения  $/U_{\delta_{b/x}}/$  возрастает по абсолютному значению и напряжение между истоком транзистора  $\mathcal{T}_2$  и подложкой. Это приводит и тому, что напряжение запирания  $\mathcal{E}_{3/2}$  этого транзистора увеличивается по абсолютному значению, что, свою очередь, уменьшает уровень выходного напряжения  $/U_{02}^{''}$  / в соответствии с формулой (1.28). Этот уровень может оказаться недостаточным для нормальной работы последующих элементов. В таком случае затвор транзистора не соединяют со стоком, а подключают к отдельному источнику смещения  $E_{CM}$ , причем  $E_{CM} > E_C$ . Тогда  $U_{02}^{"} = -E_{CM} + /E_{302}/$ , и состояние равновесия устанавливается при большой величине / " / .

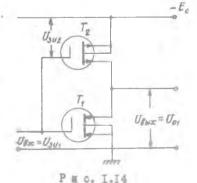

Схема кирча на транзисторах с индуцированными каналами  $\rho$  и n

Ключи на транзисторах с каналами разных типов проводимости

типа приведена на рис. I.I4. Коммутирующий транзистор  $\mathcal{T}_{i}$  имеет канат р - типа, а нагрузочный транэнстор  $T_2$  - канала n - типа. Стоки транзисторов соединены и с них снимается виходное напряжение Ибыхо Затворы также соединены друг с другом и на них подается входное напряжение  $U_{\delta x}$  . В данном случае разделение транзисторов на коммутирующий и нагрузочный условно, так как они оба управляются входным сегналом. в. таким образом, оба выполняют функцию коммутации. Подложки транзисторов 7, и 7, изолировани друг от дру-

га и поэтому оказывается возможным соединить истоки обоих транзисторов с их подложками, как показано на рис. 1.14.

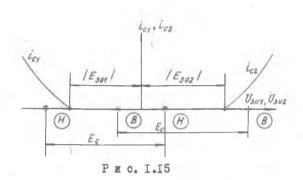

Рассмотрим работу ключа, пользуясь рис. I.15, на котором изображени статические проходние (стоко-затворние) характеристики транзисторов.

На этих характеристиках нас будут интересовать лишь точки  $E_{301}$  и  $E_{302}$ , определяющие границы между закрытым и открытым состояниями каждого из транзисторов. Заметим, что один из транзисторов всегда закрыт. Следовательно, реальные динамические характеристики транзисторов при отсутствии нагрузки практически совпадали бы с осых абсщисс. Входное отрицательное напряжение  $U_{6x}$  подается на затвор транзистора  $T_{1,9}$  т.е.  $U_{3u1} = U_{6x}$ . Напряжение между затвором транзистора

$I_2$  и его истоком, подсоединенными к источнику питания  $-E_{\mathcal{C}}$ , определяется равенством  $U_{3u\mathcal{C}}=U_{\mathcal{E}_{\mathcal{X}}}-E_{\mathcal{C}}$ , и если  $/U_{\mathcal{E}_{\mathcal{X}}}/$  не превышает  $E_{\mathcal{C}}$ , то  $U_{3u\mathcal{C}}$  всегда положительно.

Входное напряжение  $U_{\mathcal{E}_{\mathcal{X}}}$  изменяется между нижним  $U_{\mathcal{E}_{\mathcal{X}}}^{"}$  и верхним  $U_{\mathcal{E}_{\mathcal{X}}}^{"}$  уровнями. Напряжения на затворах транзисторов относительно истоков, соответствующие этим уровням, отмечены на рис. I.I5 кружками с буквами "н" и "в".

Для выключения ключа необходимо выполнение следукцих условий:

При этом транзистор  $\Gamma_1$  закрит, а транзистор  $\Gamma_2$  открит и работает в крутой области характеристик. В этом режиме сопротивление транзистора  $\Gamma_2$  мало, и выходное напряжение  $U_{\delta, \infty}$  будет облизко к  $\mathcal{E}_{c}$ . При подключении внешней нагрузки к выходу ключа через нее будет проте —

кать ток стока  $\dot{c}_{c2}$  . Для включения ключа необходимо выполнение условий:  $/U_{3U_I} / = /U_{\delta x}^{"} / > /E_{3\theta_I} /$   $U_{3U_Z} = U_{\delta x}^{"} < E_{3\theta_Z}$  (1.30)

При этом транзистор  $\mathcal{T}_t$  открыт и работает в крутой области характеристик, а транзистор  $\mathcal{T}_2$  закрыт. Выходное напряжение  $\mathcal{U}_{\mathit{быск}}$  равное остаточному напряжению на стоке  $\mathcal{T}_t$ , обизко к нулю.

Пусть напряжение источника питания  $\mathcal{E}_{c}$  выбрано так, что оно превышает по абсолютному значению напряжения запирания любого из транзисторов (  $\mathcal{E}_{301}$  и  $\mathcal{E}_{302}$  ), но меньше суммы их абсолютных значений:  $\mathcal{E}_{c} < /\mathcal{E}_{301} / + /\mathcal{E}_{302} / .$

Тогда в процессе переключения будет такое положение, когда оба транзистора закрыты. Это можно пояснить следующим.

Как видно из рис. I.I4, в рассматриваемом ключе сумма напряжений между затворами и истоками транзисторов всегда равна  $E_{\mathcal{C}}$ . Поэтому на рис. I.I5, например, точки с буквой "н" отстоят друг от другана величину  $E_{\mathcal{C}}$ , так же, как и точки с буквой "в". При увеличении  $|U_{\ell x}|$  рабочие точки для обоих транзисторов одновременно перемещаются влево из положения "в" в положение "н", оставаясь на одном и том же "расстоянии".

В процессе переключения ключа будет такое положение, когда оба рабочие точки разместятся между напряжениями запирания транзисторов  $T_1$  и  $T_2$ , и оба транзистора будут закрыты.

Аналогично при выборе напряжения источника питания  $E_c > |E_{301}| + |E_{302}|$  во время переключения создается такое положение, когда оба транзистора одновременно открыты.

В статических состояниях ключа один из транзисторов закрит, а второй открит. Следовательно, нет необходимости делать сопротивление нагрузочного транзистора  $\mathcal{T}_2$  больше, чем у  $\mathcal{T}_7$ , с целью подучения достаточно малого остаточного напряжения  $\mathcal{U}_{\delta_0/x}$ , как это было в ключе с нелинейной нагрузкой. Оба транзистора имеют примерно одинаковые параметры.

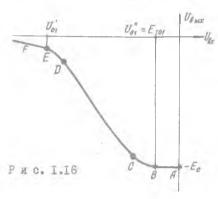

На рис. I.16 приведена характеристика передачи ключа для случая, когда  $E_c > |E_{301}| + |E_{302}|$ . На участке AB транзистор  $\mathcal{T}_{\tau}$  закрит, транзистор  $\mathcal{T}_{2}$  работает в крутой области. Когда напряжение  $|\mathcal{U}_{\delta x}|$  превзойдет значение  $|E_{301}|$ , транзистор  $\mathcal{T}_{\tau}$  открывается, напряжение  $|U_{\delta b/x}|$  начнет уменьматься, а напряжение на транзисторе  $\mathcal{T}_{2}$  увеличиваться. На` участке BC оба транзистора открити, причем  $\mathcal{T}_{\tau}$  работает в пологой области, а  $\mathcal{T}_{2}$  все еще в крутой. Линейний участок СД 6-828

соответствует состоянию, когда оба транзистора находятся в пологой области. При дальнейшем увеличении  $/U_{\ell x}/$  ( участок ДЕ) транзистор  $\mathcal{T}_1$  переходит в крутую область, а  $\mathcal{T}_2$  продолжает работать в пологой области. Когда  $U_{\ell x}$  станет равным –  $\mathcal{E}_{\mathcal{C}}$  +  $\mathcal{E}_{302}$  ( точка  $\mathcal{E}$  ), транзистор  $\mathcal{T}_2$  закроется, и на участке  $\mathcal{E}\mathcal{F}$  выходное напряжение  $U_{\ell o/x}$  практически не изменяется.

Таким образом, в этом ключе уровни включения и выключения со-

$U_{ot}' = -E_c + E_{302}$  ;  $U_{ot}'' = E_{301}$  . Соответствующие им уровни выходного надряжения

$$U_{02} = 0$$

;  $U_{02} = -E_{C}$

Для случая, когда  $\frac{U_{\theta x} = E_{101}}{U_{\theta x}} = \frac{U_{\theta x} + \left|E_{301}\right| + \left|E_{302}\right|}{E_{c} < \left|E_{301}\right| + \left|E_{302}\right|}, \text{ характеристика передачи отличается от изображенной на рис.1.16 тем, что вместо линейного участка СД существует некоторая область изменения <math>U_{\theta x}$ , в пределах которой оба транзистора закрыты, и значение  $U_{\theta 0/x}$  зависит не от  $U_{\theta x}$ , а от соотношения сопротивлений закрытых транзисторов и их тепловых токов  $U_{\theta 0/x}$  и  $U_{\theta 0/x}$

Основным достоинством ключа на транзисторах с каналами разных типов проводимости является то, что в обоих статических состояниях ( участка АВ и ЕГ ) один из транзисторов закрыт, и поэтому мощность рассеивания элементами ключа очень мала (измеряется микроваттами). Существенний расход мощности источника питания имеет место только при переключении. Очень важно также и то, что в этом ключе, как и в насищенном ключе на биполярных транзисторах, уровни выходного напряжения практически ие зависят от параметров транзистора и по-этому весьма стабильны. Наконец, рассматриваемый ключ отличается более высоким быстродействием по сравнению с ключом с нелинейной нагрузкой при одинаковых параметрах коммутирующих транзисторов и паразитных емкостях.

<u>Особенности переходных процессов в ключаж на полевых транзистораж</u>

Работа МДП - транзистора, как известно, не связана с накоплением

заряда, и поэтому собственная инерционность его чрезвычайно мала. Основной причиной, ограничивающей быстродействие ключей, построенних на МШ - транзисторах, является виляние паразитных емкостей.

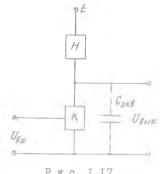

Эквивалентная схама ключа с учетом паразитных емкостей представлена на рис. 1.17.

Здесь К - коммутирующий транзистор.  $\mathcal{H}$  - нагрузка,  $\mathcal{C}_{\mathcal{J} \mathcal{K} \delta}$  - эквивалентная емкость, включающая в себя выходную емкость коммутирующего транзистора и нагрузки, а также емкость внешней нагрузки. т.е. вхолную емкость элементов, полключаемых к выходу ключа. Как было показано раньше, в ключе с нелинейной нагрузкой, состоящим из лвух транзисторов, нагрузочный транзистор всегда открыт и работает в пологой области характеристик.

Pac. I.17

Его можно рассматривать как нелинейное сопротивление, которое котя и изменяется при работе кирча, но всегда остается большим по сравнению с сопротивлением открытого коммутирующего транзистора.

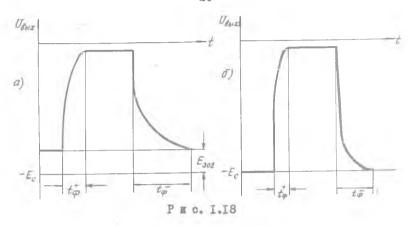

Слеповательно, быстродействие этого ключа будет определяться временем заряда и разряда  $\mathcal{C}_{\mathcal{I}\mathcal{K}\mathcal{G}}$  через  $\mathscr{N}_{\mathcal{N}}$  , где  $\mathcal{R}_{\mathcal{H}}$  - сопротивление нагрузочного транзистора. Так как  $R_H$  - нелинейно, то и заряд или разряд на всех этапах работи ключа будет происходить не по экспоненциальному закону. Кроме того, вследствие большой разности сопротивлений коммутирующего и нагрузочного транзисторов длительности фронтов положительного и отрицательного перепадов значительно отличаются друг от друга (рис. І.І8,а), т.е.  $t_{\varphi}^{+} \ll t_{\varphi}^{-}$ ,

В ключе на транзисторах с каналами разных типов проводимости, как было показано, в обоих статических состояниях один из транзисторов открыт, причем оба они имеют примерно одинаковые характеристики. Поэтому как заряд, так и разряд емкости  $\mathcal{C}_{_{\mathcal{I}\mathcal{K}}}$  происходит через открытый транзистот, и длительности фронтов  $t_{\phi}$  и  $t_{\phi}$  получаются одинаковыми и небольшими - порядка  $t_{\phi}^{\prime}$  в ключе с нединейной нагрузкой ( рыс. І.18.б).

Таким образом, ключ на транзисторах с каналами разных типов, помимо других своих достоинств, выгодно отличается и быстродействием. Заметим, что с этой точки зрения предпочтительнее режим работи ключа,

при котором оба транзистора одновременно не запираются во время переключения, т.е. когда напряжение источника питания  $\mathcal{E}_{\mathcal{C}}$  выбирается из условия  $\mathcal{E}_{\mathcal{C}} > /\mathcal{E}_{302}/+/\mathcal{E}_{302}/.$

## § I.4 . Электронные ключи на интегральных схемах (ИС)

В настоящее время в импульсную и цифровую технику, в технику управления и связи все шире внедряются интегральные ( твердосхемные ) элементи. В ИС нет отдельных дискретных деталей, а их функции выполняются определенными областями твердого тела ( кристалла полупроводника), являющимися аналогами резисторов, конденсаторов, диодов, транзисторов. Указанные области твердой схемы формируются в результате применения специальных технологических процессов.

Благодаря присутствию в ИС ненадежных межэлементных соединений ( паек, разъемов), снижению рабочих мощностей и применению прогрессивной технологии надежность ИС на порядок и более выше надежности аналогичной по назначению схемы, состоящей из дискретных элементов. В современных ИС интенсивность отказов порядка  $10^{-7} - 10^{-8}$  1/час.

Структура ключей ИС не отличается от структуры рассмотренных выше ключей на дискретных элементах. В настоящее время имеется очень больной набор ИС, работающих в ключевом режиме и отличающихся другот друга схемной реализацией, а также видом связей между элементами.

Все ключевые схемы выполняют логические функции входных сигналов типа HE - WIN ( или HE - N ).

Основными характеристиками ключей ИС, помимо надежности и стоимости, являются следующие:

поротовые уровни ключа, т.е. уровни входного, управляющего напряжения ( или тока), при которых происходит переключение ключа из состояния " о " в состояние "I " и наоборот;

нагрузочная способность ИС характеризуется коэффициентом разветвления по выходу  $n_{\delta x}$ , который определяет, каким числом аналогичных ключей ИС может быть нагружен данный ключ ИС;

коэффициент объединения по входу  $m_{\delta x}$ , который определяет максимальное число входов ключевой схемы;

быстродействие ключа ИС карактеризуется средним временем задерики  $t_{\scriptscriptstyle CD}$  , определяемым величиной

$t_{3C\rho}=\frac{1}{2}\left(t_{\delta NA}+t_{\delta ONA}\right)$ . где  $t_{\delta NA}$ ,  $t_{\delta ONA}$ — соответственно длительности включения и выключения ключен.

потребляемая мощность.

Здесь различают схемы с большой средней, малой и весьма малой мощностью рассеяния.

Так как все эти ключи ИС выполняют логические функции, то они подробно рассматриваются в следующей главе.

## Литература

- I. Гольденберг Л.М. Импульсные и пифровые устройства. М., "Связь", 1973.

- 2. Гусев В.В., Зеличенко Л.Г. и др. Основы импульсной и цифровой техники. М., " Сов. радио", 1975.

- 3. Степаненко И.П. Основи теории транзисторов и транзисторных схем. М., "Энергия", 1973.

- 4. Агаханян Т.М. Электронные ключи и нелинейные импульсные усилители. М., "Сов. радио", 1966.

- 5. Ицкоки Я.С., Овчинников Н.И. Импульсные и пифровые устройства. М., "Сов.радно", 1972.

- 6. Фролкин В.Т. Импульсные устройства. М., " Машиностроение", 1966.

### Глава П. ПОТЕНЦИАЛЬНЫЕ ЛОГИЧЕСКИЕ И АНАЛОГОВЫЕ ЭЛЕМЕНТЫ ИМПУЛЬСНЫХ УСТРОЙСТВ

#### § 2.1. Основные характеристики логических элементов

Интегральные схемы (ИС) потенциального типа являются самыми распростратенными микроэлектронными логическими схемами. Они выгодно отличаются от импульсных логических схем, так как, имея связь между входом и выходом по постоянному току, ИС потенциального типа наилучшим образом соответствует возможностям микроэлектронной технологии.

Непрерывно растет степень интеграции ИС и сложность выполняемых функций. Несмотря на большое количество ИС потенциального типа их схемотехническая реализация осуществляется на основе ряда типовых, базовых функциональных элементов.

К основным параметрам, характеризующим возможности базовых элементов, как уже отмечалось в § 1.4, относятся : реализуемая функция, нагрузочная способность  $n_{\ell x}$  ( или n ), коэффициэнт объединения по входу  $m_{\ell x}$  ( или m ), средняя задержка передачи сигнала  $t_{3a\partial}$ , предельная рабочая частота  $f_{\rho}$ , помехоустойчивость и потребляемая мощность.

По виду реализуемой функции элементы ИС условно могут быть разбиты на два класса.

К первому классу относятся функциональные элементы одноступенчатой логики. Это простейшие логические элементы, реализующие функции И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ.

Ко второму классу относятся функциональные элементы двухступенчатой логики, реализующие более сложные функции И-ИЛИ, ИЛИ-И, НЕ-И-ИЛИ, И-ИЛИ-НЕ, И-ИЛИ-И и др.

Нагрузочная способность догических элементов n определяет количество элементов (точнее их входов), которые можно подключить к выходу данного элемента. При этом должна обеспечиваться неискаженная передача сигналов 0 и 1 при наихудших сочетаниях дестабилизирующих факторов. В ряде случаев этот параметр называется коэффициентом разветвления, исходя из его физического смысла. Следовательно, n есть целое положительное число (n = 4, 5, 7, 10 и т.д.).

Чем выше нагрузочная опособность, т.е. чем больше n, тем богаче функциональные возможности ИС.

Козфилиент объеминения по входу m характеризует максимальное число логических входов иС. Увеличение m обично ухудшает другие параметри иС, такие как бистродействие, помехоустойчивость и т.д. В выпускаемих иС обично m=2-6. Увеличение числа m (числа входов) происходит обычно за счет так называемого расширителя, входящего в эту серию иС. Это дает возможность увеличить m до 10.

Линамические параметры догических элементов. Сида относятся:

$t_{\omega_1}$  - фронт формирования логической " I ";

$t_{agg}$  - фронт формирования логического " 0 ":

$t_{10}^{\prime}$  — задержка ( время) переключения ИС из состояния " I " в состояние " 0";

$t_{ot}$  — задержка переключения из состояния " 0" в состояние "I";

$t_{\mu}$  - длительность импульса;

$f_{\rho}$  - рабочая чистота.

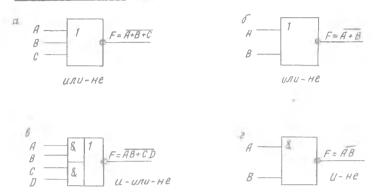

Согласно Единой Системе Конструкторской Документации (ЕСКД) и ГОСТ 2743-72 приняты следующие обозначения функциональных элементов (рис. 2.1):

символ & — энд — обозначает функцию "  $M^m$ ; символ I — обозначает функцию "  $MIM^m$ . Инверсий обозначается кружком.

P M C. 2.I

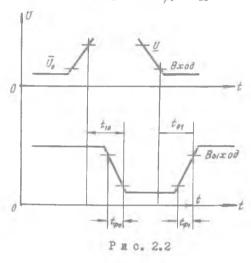

На рис. 2.2 приведени характеристики сигналов на входе и выходе логического элемента ( инвертора) и показаны уровни отсчёта, относительно которых определяются динамические параметры.

Уровнями отсчета динамических параметров логического элемента для приведенной на рис.2.2 положительной логичи являютоя максимальный уровень логической " I ". Задержка переключения  $t_{10}$  определяется как временной интервал между уровнем " I " фронта нарастания входного импульса ( положительный импульс) и уровнем " 0" фронта спада выходного импульса (отрицательный импульс). Задержка переключения  $t_{10}$  определяется как временной интервал между уровнем "0" фронта спада входного импульса и уровнем "1" фронта нарастания выходного импульса. Фронти импульса, оп-

ределяемые между уровнями " I " и " 0 " спада импульса, обозначаются  $t_{\varphi_0}$  , между уровнями " О" и " І " нарастания импульса –  $t_{\varphi_0}$  . Длительность импульса на выходе элемента определяется временным интервалом между фронтом  $t_{\varpi \rho}$  и фронтом  $t_{\varpi t}$  на уровне " I ".

Средняя задержка  $t_{c\rho}$  логического элемента определяется как полусумма задержек  $t_{10}$  и  $t_{01}$  и служит усрепненным параметром быстролействия, используемым при расчете временных характеристик многоэлементных последовательно включенных догических CX6M.

Параметр

Параметр

$$t_{c\rho} = \frac{t_{l0} + t_{ol}}{2} \qquad (I.I)$$

приводится в технических условиях на интегральные схеми. Для упрощения расчетов часто считают сигналы прямоугольными, т. е. полагают  $t_{\phi o} = t_{\phi l} = 0$

Помехоустойчивость. Базовый элемент интегральной схемы в статическом режиме может находится в одном из двух возможных состояний ("О" или "І"). По этой причине различают статическую помехоустойчивость ИС по уровню "О" (  $U_{\alpha_{\ell}}$  ) и по уровню I (  $U_{\alpha_{\ell}}$  ). Статическая помехоустойчивость базовых элементов ИС определяет величину напряжения, которое может быть подано на вход интегральной схемы относительно уровня " 0" или " I ", не вызывая ее ложного срабатывания (например, переход из состояния " I " или в состояние " O" или обратно).

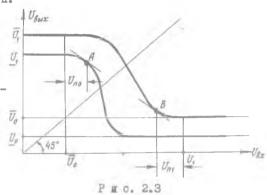

Значение параметра  $U_{\alpha\rho}$  и  $U_{\alpha\rho}$  определяют из анализа семейств передаточных характеристик функциональных элементов интегральных схем. На рис. 2.3 приведени передаточные карактеристики функционального элемента (ПХЭ), выполняющего функцию инверсии НЕ, и показаны точки, относительно которых определяется статическая помехоустойчивость скемы по уровню " 0" ( $\mathcal{V}_{n,\theta}$ ) и по уровню " I " ( $\mathcal{V}_{n,\theta}$ ). Параметр  $\mathcal{V}_{n,\theta}$ определяется как разность напряжений точки А. соответствующей месту перегиба нижней кривой ПХЭ, и максимального уровня "0" ( $\overline{U}_{R,q}$ ). Параметр  $U_{a_1}$  определяется как разность напряжений минимального уровня

" I " (  $\underline{U}_t$  ) и точки B , соответствующей месту перегиба верхней кривой ПХЭ.

Верхняя и нижняя кривые ПХЭ являются огибающими семейства передаточных карактеристик инвертирующего элемента, полученных с учетом "худших условий его работы" — при изменении температуры, питающих напряжений, нагрузки и т.п.

Однако статическая помехоустойчивость не дает полной информации об устойчивой работе элемента в устройстве, так как не характеризует помехоустойчивость в динамическом режиме работы.

Динамическая помехо - устойчивость - помехоус - тойчивость в динамическом режиме - зависит от дли-тельности, амплитуды и

формы сигнала помехи, а так же от уровня статической помехоустойчивости и скорости переключения базового функционального элемента.

При воздействии коротких импульсов помехи схеми с низкой статической помехозащищенностью и бистродействием могут бить более помехоустойчиви, чем схеми с достаточно високим уровнем статической помехозащищенности и бистродействием. Другими словами, високая статическая помехозащищенность не определяет високую динамическую помехоустойчивость функционального элемента.

Сложность получения характеристик динамической помехоустойчивости элементов не позволяет в настоящее время приводить их в качестве эсновного или справочного материала в технических условиях на интегральные схемы.

<u>Потребляемая мощность</u>. При работе в реальных условиях каждая логическая схема может находиться в следующих состояниях:

- " выключено":

- в стадии включения:

- в состоянии " включено":

- в сталии выключения.

- В каждом из этих состояний элемент потребляет от источника раз-

8-828

личную мощность. При этом в зависимости от типа логического элемента некоторне из них большую мощность потребляют в статических состояниях включено и и выключено и сравнительно незначательную во время переходного процесса из состояния включено в состояние вних лючено и наоборот. Другие характеризуются большей потребляемой мощностью во время переходных процессов и относительно невысокой — в статических состояниях.

По потребляемой мощности ИС подразделяются: на мощные логические схемы ( 25 мвт <  $\rho_{nomp}$  < 250 мвт); схемы средней мощности ( 3 мвт <  $\rho_{nomp}$  < 25 мвт); маломощные схемы ( 0,3 мвт <  $\rho_{nomp}$  < 3 мвт ); микроваттные схемы ( I мквт <  $\rho_{nomp}$  < 300 мквт); нановаттные схемы (  $\rho_{nomp}$  < I мквт ).

Как правило, наиболее мощные схемы обледают и большим быстро-

## § 2.2. Интегральные схемы одноступенчатой логики

Интегральные схемы потенциального типа с одноступенчатой логикой по схемотехнической реализации делятся на следующие виды: резистивно-транзисторные ИС ( RT4):

транзисторные ИС с непосредственной связыю между логическими элементами (DCTL);

транзисторные ИС с резистивными связями между логическими элементами (TRL);

транзисторные ИС с резистивно-емкостными связями между логическими элементами ( RCTL );

диодно-транзисторные ИС (ДГА);

транзисторные ИС с эмиттерными связями между догическими элементами (  $\mathcal{E}$   $\mathcal{CL}$  ).

Резистивно-транзисторные ИС ( RTL)

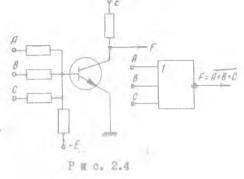

На рис. 2.4 показани функциональная и электрическая сжеми логического элемента ИС типа РГА, реализующего операцию ИИИ — НЕ. Здесь операция ИЛИ осуществляется на резистивной сборке, а транзистор выполняет роль инвертора. Основной недостаток сжеми состоит в том, что для ее резистивной части требуются высокоомные и высокоточные резисторы. Это вызывает трудности при изготовлении. Кроме того, резисторная сборка ИЛИ потребляет относительно большую мощность от источников. В силу слабой "развязки" входов, схема обладает низкой помехоза-

цищенностью. Для ИС данного типа жарактерна малая

нагрузочная способность

( n < 3 ) я низок коэффациент объединения по

входу ( m или < 3 ).

Транзисторные ИС с непосредственной, резистивной и резистивно-емкостной связыю ( DCTL . TRL . RCTL ).

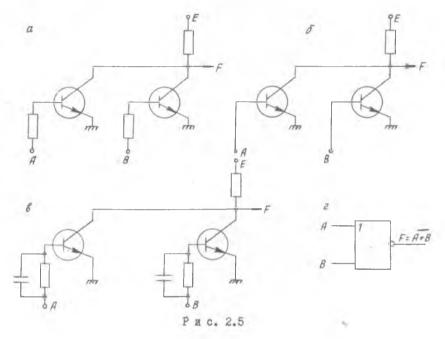

На рис.2.5 приведены схемы логических элементов DCTL, TRL и RCTL, выполняющих функцию ИЛИ-НЕ.

Транзисторные ИС с непосредственными связями нашли широкое применение и являются одним из основных схемотехнических направлений. Схемы DCTL характерны тем, что на их параметры сильно влияет разброс входных характеристик транзисторов. Для схем  $DCTL \, m > 8$ , а n < 4. Они обладают низким уровнем помехозащищенности, но хорошим быстродействием (  $t_{CP} = 5-10$  нс).

Схемн RCTL не получили распространения из—за сложности их изготовления, так как создание емкостей в интегральном исполнении — запача сложная.

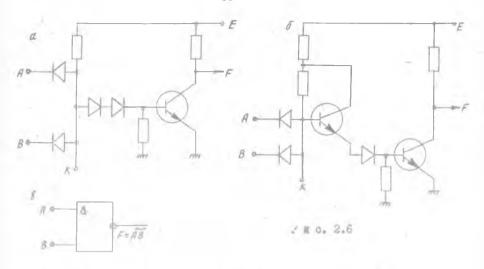

Диодно-транзисторные ИС ( DTL )

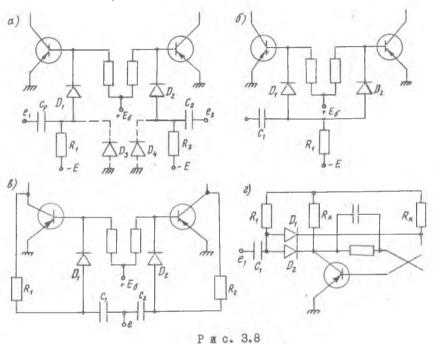

Базовые функциональные элементы (рис. 2 — 6) диодно-транзистерных схем реализуют логическую функцию И-НЕ (для положительной логики). Функцию "И" выполняют на диодной группе, а функцию усилителя -инвертора — на транзисторах.

Известны две наиболее распространенные группы *DTL* - схем. В первую входят схемы с однотранзисторным усилителем на выходе ( рис. 2.6,a), вс вторую - с усилителем на составном транзисторе (рис. 2.6,d). Применение усилителя на составном транзисторе позволяет снизить

требования к коэффициенту усиления интегральных транзисторов. Схемы DTL обладают большим значением коэффициента объединения до входу ( $m_H > 10$ ) и высокой нагрузочной способностью (n = 7-10)

У диодной части схемы предусматривается вывод общего анода (К), который служит для подключения логического расширителя "И". Предельное быстродействие DTL-ИС  $t_{c\rho}=10-20$  нс;  $t_{\rho}$  — до 20 мГц. Уровень помехозащищенности в 2-3 раза превосходит уровень помехозащищенности схем транзисторной логики.

Общим свойством рассмотренных *RTL*, *TRL*, *RCTL*, *CTRL*, *DTL* интегральных схем является использование нелинейного режима работы активных элементов. Усилители рассмотренных ИС характеризуются надежным запиранием транзисторов в одном логическом состоянии и насыщением — в другом.

Режим насыщения не позволяет использовать высокие частотные свойства транзисторов в интегральном исполнении из-за явления рассасывания избыточного заряда в базе.

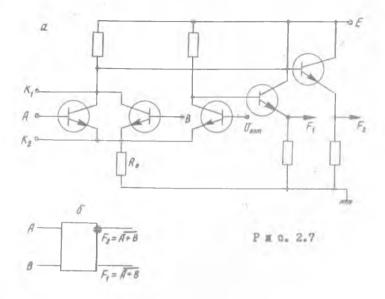

# MC o searreposes onesses (ECL)

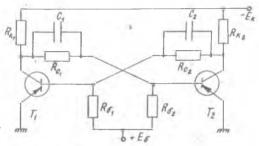

Отличательной чертой ИС с эмиттерними связями ( рис. 2.7) явияется ненасищенний режим работи транзисторов, что обеспечивает их високое бистродействие. Схема ECL (рис.2.7,а) выполняется на двух переключателях тока. Один из них, нормально открытий, реализован на

транзисторе, на бабу которого подано отпирающее напряжение  $U_{om}$ .

Уровень  $U_{om}$  ниже минимального уровня логической единицы. Второй переключатель тока состоит из m ( по чиску логических входов) транэисторов, имеющих общие комлекторы и эмиттеры, что обеспечивает реализацию функции " ИЛИ". Открывание любого из транзисторов второго

переключателя тока повышает напряжение на общем эмиттерном сопротивлении  $R_o$  и обеспечивает запирание первого переключателя тока, что

приводит к формированию на выходе  $F_f$  высокого уровня (догическая

"I"), в то время как на выходе  $F_2$  формируется низкий уровень напряжения ( догический " 0").

Нагрузочная способность этих схем достаточно велика ( $^{72}$  10). Наличие вхота  $\mathbf{L}_1$  и  $\mathbf{K}_2$  позволяет расмирить число входов ИЛИ, правда, при этом сывкается быстродействие. Для сбеспечения высокой нагрузочной способности в состав серий ECL – ИС включаются схемы с мощным выходом, обеспечивающие значение n > 30.

### § 2.3. Интегральные схемы двухотупенчатой логики

По схемотехнической реализации схемы двухступенчатой логики можно разделить на диодно-транзисторные ИС -(DTL-2) транзисторно-транзисторные ИС -(TTL) транзистор-транзисторно-транзисторные ИС--(T-TTL).

Диодно-транзисторные ИС ( DTL-2 ).

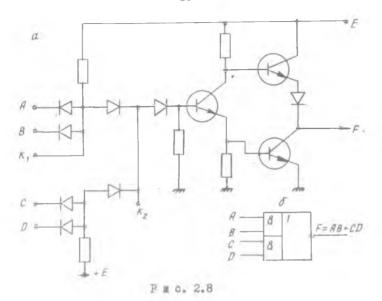

На рис. 2.8 приведена схема функционального элемента диоднотранзисторной логики, реализущая двухступенчатую функцию И-ИЛИ-НЕ. Реализация логической операции и и ИЛИ в схемах DTL-2 осуществинется на диодах, а операции НЕ выполняется на транзисторном усилителенняерторе. Для увеличения логических возможностей схем по входам и иЛИ применяются специальные расширители функций и и ИЛИ (входи  $K_{\rm L}$  и  $K_{\rm L}$ ). Схемы DTL-2 имеют  $m_u > 8$ ,  $m_{unu} > 6$ . Выходной усилитель схемы выполняется с симметричени транзисторным выходом, благодаря которому нагрузочная способность  $n > \delta$ .

Диодно-транзасторные интегральные схемы были наиболее важным достижением микроэлектроники середины 60 годов.

Транзистор-транзисторные ИС - ( ГТ / )

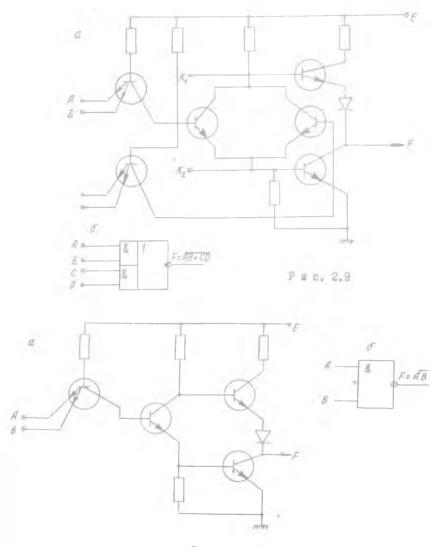

Освоение технологии изготовления многозмиттерного транзистора (МЭТ) послуживо определяющим фактором в создании инрокого ряда серий интегральных схем  $\Gamma \Gamma L$  логики. Многозмиттерный транзистор (МЭТ) представляет собой интегральный элемент, объединяющий преммущества диодных логических схем и транзисторного усилителя.  $\Gamma \Gamma L$  схемы (рис. 2.9) позволили значительно увеличить бистродействие  $t_{C\rho} = 3-10$  нс), повысить уровень помехозащищенности, снизить потребляемую мощность по сравнению с  $D\Gamma L$  – ИС, а также увеличить функциональные возможности интегральной схемы. Коэффициент  $m_{u,v} = 12-14$

Выходине услантели 772 — схем обеспечивают высокую нагрузочную способность базовой схемы ( n > 10 ).

В состав существующих серві 77/2 — ИС входит вирокий функциональный набор следующих микроскем:

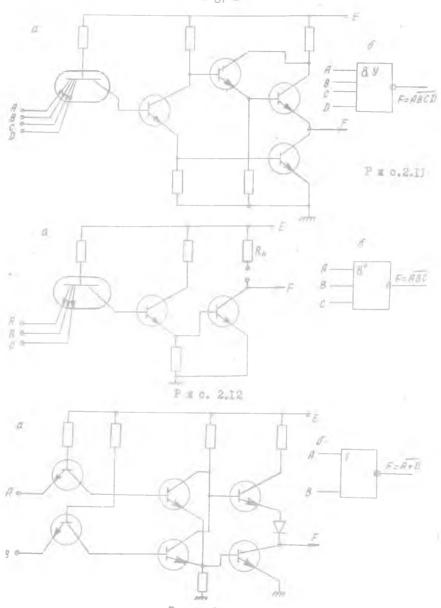

схемы И-НЕ (рис. 2.10); схемы И-НЕ с мощным выходом (рис. 2.11); схемы И-НЕ со свободным коллектором (рис. 2.12); схемы ИЛИ-НЕ (рис.2.13);

10-828

P m c. 2.10

P m c. 2.13

схемы ИЛИ с двухкаскадным усилителем:

скеми И с двухкаскалным усилителем:

схемы И с двухкаскадным усилителем со свободным коллектором; схемы И-ИЛИ-НЕ:

логические расширители И-ИЛИ (рис.2.14)

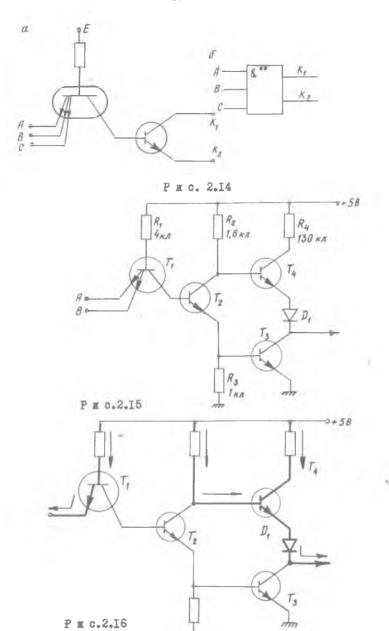

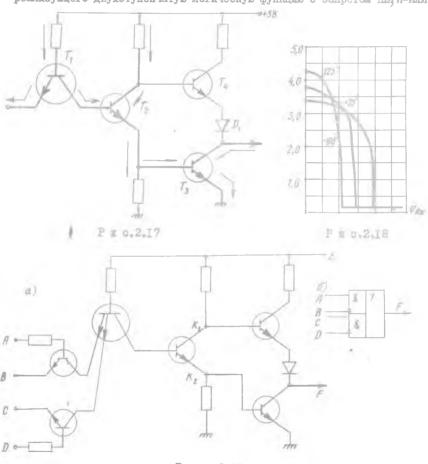

Широкий функциональный состав серий TTZ— ИС позволяет вести разработку цефровых узлов с использованием различных сочетаний типовых ИС. Схемы TTZ обладают большой нагрузочной способностью ( n>25 ) и высоким быстродействием. Так как схемы TTZ получили широкое распространение, то рассмотрим основной элемент TTZ более подробно. На рис. 25 представлена принципиальная схема базового элемента TTZ с номиналами сопротивлений и источником питания.

При наличии на одном из входов (A, B) логического " 0"  $T_1$  насыщен,  $T_2$  и  $T_1$  выключены,  $T_2$  открыт, и ток идет в нагрузку (рис.2.16).

Выходное напряжение логической "I" отличается на малую величину му от источника питания ( на величину двойного падения напряжения на  $\rho-\rho_2$  — переходе  $T_4$  и  $D_7$  . Если на всех входах появляется логическая "I",  $T_7$  выходит из насыщения в инверсно-активную область,  $T_2$  переходит в активное состояние, выходное напряжение падает. При дальнейшем увеличении входного напряжения транзисторы  $T_2$  и  $T_3$  открываются, входят в насыщение и закрывают  $T_4$  . Выходное напряжение "0" равно напряжению насыщения  $T_5$ . Таким образом,  $T_2$  образует "фазорасщепитель",  $T_3$  и  $T_4$  образуют выходной каскад с повышенной нагрузочной способностью. На рис. 2.17 показано распределение токов в включенной схеме. Для этой интегральной схеми выходное сопротивление в состоянии " $T_6$  "равно  $T_6$  = 134 Ом, в состоянии " $T_6$  " - это сопротивление насыщенного транзистора  $T_3$   $R_{Hac}$  = 15 Ом. Входное сопротивление при " $T_6$  " на входе  $R_{for}$  = 100 кОм, при " $T_6$  "  $R_{for}$  = 4 кОм.

$U_{\delta_{\theta/X}}^{2} \le 0.35B$ ;  $U_{\delta_{\theta/X}}^{2} \ge 2.4B$ ; n = 10. Передаточная характеристика приведена на рис. 2.18. Неиспользуемые входы схемы можно включать следующим образом:

замыкать с используемыми. В этом случае ИС обладает максимальным быстродействием, но возрастает потребляемый ток;

оставлять свободными. При этом снижается помехоустойчивость, но это самый простой метод с точки зрения монтажа;

подсоединять к шине питания.

Для построения импульсных и цийровых устройств чаще всего используются 2-х входовые (4 в корпусе), 3-х входовые (3 в корпусе) и 4-х входовые (2 в корпусе) интегральные схемы.

Транзистор-транзисторно-транзисторные ИС - (Г-ГГС)

Интегральные схемы 7-772 логики относятся к разряду новых логических микросхем, выполненных на основе модернизации существующих ГГС - схем. На рис. 2.19 приведена базовая схема элемента 7-77%, реализующего двухступенчатую логическую функцию с запретом НЕ, И-ИЛИ.

P m c. 2.19

Логическая операция и о запретом выполняется на транзисторах, управляемых по базе и эмиттеру, а функция ИЛИ реализуется на мно-гозмиттерном транзисторе. Наличие запрещающего входа по эмиттеру в схеме И открывает новые возможности при построении цифровых устройств на основе совместного использования схем 7-772 и 772, ко-торые имеют электрическое согласование.

T-T/Z- ИС имеют хорошую нагрузочную способность; наличие прямых и инверсных входов позволяет исключить ряд промежуточных инверторов при реализации сложных функций. Недостатком T-T/Z- ИС надосчитать снижение уровня статической помехозащищенности и увеличение задержки переключения при управлении по прямому (базовому) входу схему НЕ, И.

#### 6 2.4. Логические схемы на полевых транэисторах

Как уже отмечалось выше, полевые транзисторы являются наиболее перспективными полупроводниковыми приборами, открывающими новые возможности в области создания интегральных схем большой и сверхбольшой интеграции. В настоящее время наибольшее распространение получили логические схемы на транзисторах с МДП-структурой.

Логические схеми на МДП - транзисторах  $\rho$  - типа

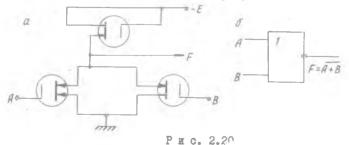

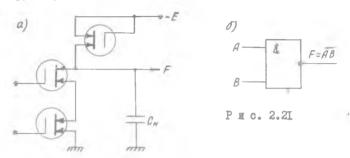

Принципы построения логических схем на МДП-транзисторах одного типа проводымости сходны с принципами построения логических схем с непосредственными связями ( DCTL ).

На рис. 2.20 приведена скема ИЛИ-НЕ на два входа, содержащая один нагрузочный транзистор и два логических. Интегральная технология МДП-структур позволяет использовать последовательное (ярусное) включение МДП-транзисторов, когда в цепь между

нагрузкой и землей включен не один, а два и более МДП-транзисторов по схеме "И". В этом случае исток нижнего легического транзистора подключается к земле, а его сток к истоку выпестоящего и т.д.

Путь току через нагрузку к земле откривается лишь в том случае, если будут открити транзистори всех ярусов. На рис. 2.21 приведена подобная схема, реализующая логическую функцию И-НЕ, имеющая високую нагрузочную способность.

Ярусное включение позволяет создавать логические схемы, обладающие большей универсальностью, чем схемы на биполярных транзисторах.

На рис. 2.22 представлени сложные логические схемы МДП-ИС –  $\rho$  – типа, реализующие функции ИЛИ-И-НЕ (рис.2.22,а), И-ИЛИ-НЕ (рис.2.22,б) и ИЛИ-И-ИЛИ-НЕ (рис. 2.22,В).

Логические схеми на МДП-транзисторах обладают очень высокой нагру-зочной способностью ( n>10 – 20) и относительно хорошим быстродействием,  $f_{p}\approx 1$  МГу $_{0}$

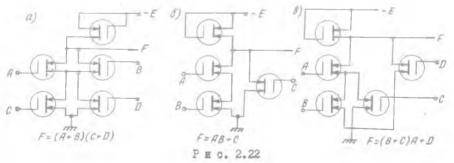

Логические схемы на дополняющих МДП-транзисторах (МДПДТ-ИС)

Догические схемы на МДПДТ обладают очень хорошими показателями: макроваттной потребляемой мощностью в статическом режиме; высоким быстродействием;

высокой помехоустойчивостью за счет большого перепада уровней сигналов логических "I" и " 0":

новыми логическими возможностями за счет взаимодополняющих структур.

Логические схемы МДПДТ отличаются тем, что для каждого логического входа необходимо применять транзистор  $\rho$  — типа и связанный с ним по затвору транзистор  $\rho$  — типа.

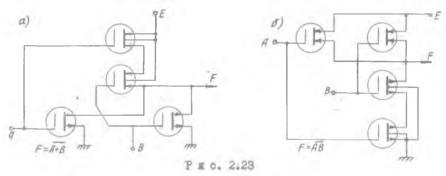

На рас. 2.23 пряведены двухвходовые схемы ИЛИ-НЕ и И-НЕ положительной логики на МДПДТ.

При поступлении на вход A ( схема ИЛИ-НЕ, рис. 2.23,а) сигнала " I " ( напряжение, близкое k+E ) откроется транзистор  $\rho$  - типа, а связанний с ним по затвору транзистор  $\rho$  - типа закроется. На выходе схемы формируется уровень " 0", близкий к потенциалу "земли". Когда на входа A и B будут поданы одинаковые уровни " 0 ", то оба транзистора  $\rho$  - типа закроится и откроится оба транзистора  $\rho$  - типа, что приведет к формированию на выходе уровня " I ", близкого  $\kappa + E$ . Так как  $\kappa$  состоянии  $\kappa = 0$  открыт транзистор  $\kappa$  - типа, а  $\kappa$  состоянии  $\kappa$  = I открыт прибор  $\kappa$  - типа, перезарад емкости нагрузки ( паразитной емкости) всегда осуществляется через открытий прибор МЛП - транзистор.

Логические схемы на МДПДТ с нагрузочным транзистором (МДПДТ-ИС)

Применение в качестве нагрузки МДП-транзистора еще больше расширяет возможности интегральных схем на МДП-транзисторах. Здесь можно реализовать как положительную логику (в этом случае в нагрузке

применен транзистор р — типа), так и отрицательную (нагрузка —

транзистор л — типа). Сочетание дополняющих транзисторов с нагрузочным позволяет реализовать сложные логические функции с минимум

компонентов.

#### § 2.5. Аналоговне интегральные схемы

Операционные усилители

Помимо цифровых интегральных схем отечественная промышленность выпускает ряд аналоговых схем в интегральном исполнении — это двух-каскадные, дифференциальные, операционные усилителы (ОУ). Наиболее универсальным из этой группы схем является операционный усилитель. На его основе могут быть построены самые разнообразные устройства.

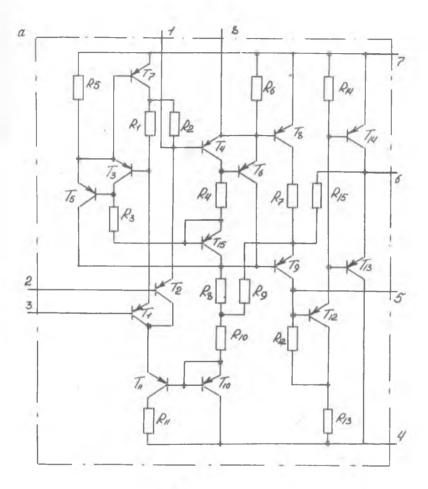

Операционный усилитель — это усилитель постоянного тока с достаточно большим коэффициентом усиления. В настоящее время вниускается большое число разновидностей ОУ в интегральном исполнении. Однако различая в их построении и характеристиках не слишком велики. Поэтому рассмотрим схему интегрального ОУ на примере усилителя КГУТ 531 рис. 2-24,а.

Усилитель содержит два дифференциальных усилительных каскада и выходной каскад. Первый дифференциальный каскад включает транзистори ТІ и Т2 и работает в режиме маных токов ( комлекторные токи транзисторов около 20 мкА). Благодаря этому обеспечивается высокое входное сопротивление усилителя и малый дрейф нуля. Для того, чтобы каскад усиливал только разность напряжений на входах, а не сами напряжения, эмиттеры входящих в него транзисторов подключены к генератору тока на транзисторе ТІІ. Напряжения на базу транзистора ТІІ подается с базо-эмиттерного перехода транзистора ТІО, используемого в качестве диода. При этом обеспечивается стабилизация коллекторного тока транзистора ТІІ в широком диапазоне температур.

Режим малых токов не позволяет получить большое усиление в первом каскаде, поэтому основное усиление производится во втором каска-

Рис. 2.24

де, который построен на основе составных транзисторов ТЗ, Т5-и Т4,Т6. Транзистор ТІ5 стабилизирует работу каскада при изменении температуры.

К выходам второго каскада присоединены два эмиттерных повторителя, выполненные на транзисторах Т7 и Т8. Через транзистор Т7 подается питание на первый каскад, а через транзистор Т8 осуществляется передача сигнала на выходной каскад.

Выходной каскад содержит усилитель с общей базой (транзистор Т9), усилитель с общим эмиттером (транзистор Т12), эмиттерный повторитель (транзисторы Т13, Т14).

Интегральная схема усилителя КІУТ531 имеет восемь выводов. К выводам 7 и 4 подключаются положительный и отрицательный источники питания. Выводы 1,5 и 8 — вспомогательные для подключения корректирующих цепей. Вывод 6 — выход усилителя, а выводы 2,3 — его входы. При уменьшении напряжения на входе 2 и увеличении напряжения на входе 3 выходное напряжение увеличивается. Поэтому вход 2 называют инвертирующим ( И — входом), а вход 3 — неинвертирующими ( Н — вход).

На принципиальных схемах ОУ обычно изображается в виде треугольника с обозначениями двух входов и одного выхода ( рис. 2,24,6).

И — вход и Н — вход обозначаются знаками "" и "+" соответственно. Операционные усилители характеризуются большим числом параметров. Рассмотрим основные из них.

Коэффициент усиления (К) — отношение выходного напряжения к вызвавшему его изменению дифференциального входного напряжения, т.е. к напряжению между входами усилителя. Величина К лежит обычно в пределах  $10^3-10^5$ .

Ширина частотной полосы ОУ (  $f_m$  ) определится частотой, на которой коэффициент усиления падает до единицы. Значения  $f_m$  обычно составляют 10 кГц — 10 МГп.

Средний входной ток ( $\mathcal{I}_{\ell,x}$ ) — среднее арифметическое значение токов по двум входам, измеренных при условии, что напряжение на выходе ОУ равно нулю. Чаще всего  $\mathcal{I}_{\ell,x}=0$ , I — I ОмкА.

Разность входных токов ( $\Delta J_{\ell x}$ ) — разность токов по двум входам при равенстве нулю выходного напряжения. Обично  $\Delta J_{\ell x}$  =0,I — 5мкА.

Напряжение смещения (  $U_{CM}$  ) — напряжение, которое нужно приложить между входами для получения нуля на выходе.  $\Delta U_{\delta x}$  =0.5 — 10 мВ.

Максимальное синфазное входное напряжение (  $U_{c\phi}$  ) — допустимое значение напряжений, прикладываемых одновраменно к обоим входам, при котором усилитель сохраняет свои характеристики. Обычно  $U_{c\phi} = I - I0$  В.

Коэффициент ослабления синфазного сигнала (  $\mathcal{M}_{\mathcal{C}\phi}$  )— отношение коэффициента усиления усилителя к коэффициенту передачи синфазного

сигнала. Коэффициент передачи синфазного сигнала определяется ках отношение изменения выходного напряжения к вызвавшему его изменению синфазного входного напряжения при постоянстве разности напряжений между входами. Величина  $\mathcal{M}_{\mathcal{C}_{\mathcal{O}}}$  составляет обично 60-100 дБ.

Входное сопротивление ( $\mathcal{R}_{\ell x}$ ) — сопротивление со сторони любого входа, когда другой вход заземлен. Входное сопротивление для дифференциального сигнала составляет обычно от  $10^3$  до  $10^6$  см. Входное сопротивление для синфазного сигнала на 1-2 порядка больше.

Выходное сопротивление ( $\mathcal{R}_{\delta_{b/x}}$ ) — сопротивление со стороны выхода, когда напряжение на выходе равно нулю. Для разных типов выходных каскадов выходное сопротивление меняется в пределах 25-500 см.

Максимальное выходное напряжение (  $U_{f_0/x}$ ) – амплитуда выходного напряжения при работе ОУ на линейном участке.  $U_{f_0/x} = \frac{1}{3} - 13$  В.

Максимальная скорость нарастания виходного напряжения (  $U_{\delta_0/X}$  ) определяется как наибольшее значение скорости изменения напряжения на выходе ОУ при подаче на его вход импульса максимально допустимого входного напряжения прямоугольной формы. Обычно эта скорость лежит в пределах  $0.1-20~\mathrm{B/mrc.}$

Максимальный выходной ток ( $\mathcal{I}_{\ell_{\theta}/x}$ ) — максимальный ток в нагрузке уселетеля, не вызывающий выхода его из строя.  $\mathcal{I}_{\ell_{\theta}/x}$  = I — IO мА.

Коэффициент влияния источников питания ( $U_{\alpha}$ ) — отношение изменения напряжения смещения к изменению питающего напряжения  $U_{\alpha}$  = = 20 — 200 мкВ/В.

Потребляемая мощность (  $P_{\alpha}$  ) — мощность, рассеиваемая в усилителе при нулевом напряжении на выходе и отсутствии тока в нагрузке. Для типовых ОУ  $Pn \pm 70 - 150$  мВт.

Температурный дрейф напряжения смещения (  $U_{\partial\rho}$  ) — отношение изменения напряжения смещения к вызвавшему его изменению температуры окружающей среды. Обычно  $\Delta U_{\partial\rho}$  не превышает 5—20 мкВ/град.

#### Литература

- I. Букреев И.Н. и др. Микроэлектронные схемы цифровых устройств. М., "Сов. радио", 1975.

- Проектирование радиоэлектронных устройств на интегральных микросхемах. Под ред. Шаца С.Я. М., "Сов. радио", 1976.

- 3. Скарлетт Дж. Транзисторно-транзисторные логические схемы и их применение. Пер. с англ. М., "Мир", 1974.

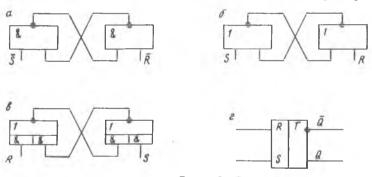

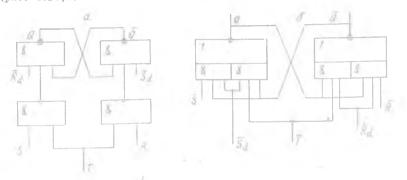

#### глава Ш. ТРИГГЕРЫ

#### § 3.1. Общие сведения о триггерах

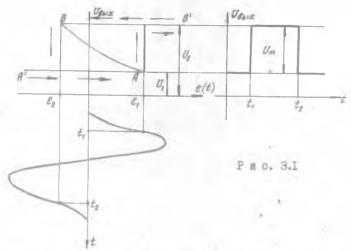

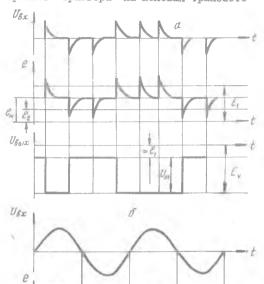

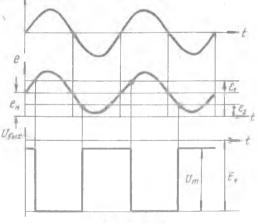

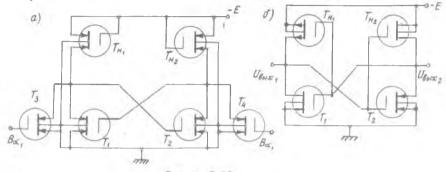

Триггером называется спусковое устройство, которое может неограниченно долго находится в одном из двух электрических состояний устойчивого равновесия и переходить из одного в другое скачком воякий раз, когда воздействующее на его вход управляющее напряжение e(t)достигает некоторых фиксированных пороговых уровней  $\mathcal{E}_r$  и  $\mathcal{E}_z$ . Зависимость выходного напряжения  $\mathcal{U}_{\mathcal{E}_{\phi/X}}$  триггера от входного управляющего напряжения e(t) имеет форму гистерезисной петли (рис.3.1).

Нижняя A'A' и верхняя B'B ветви характеристики  $U_{\delta o/A'} = f(e)$  соответствуют двум устойчивым состояниям равновесия триггера, а точки A' и B' — пороговым значениям управляющего напряжения. На падающем участке B'A', где кругизна характеристики отрицательна, равновесие системы неустойчиво.

При возрастании напряжения e(t) ( по нижней ветви AB ) виходное напряжение  $U_{6,lx}$  остается постоянным и равным  $U_t$  до момента, когда управляющее напряжение e(t) достигнет порогового значения  $\mathcal{E}_t$ , при котором напряжение  $U_{6,lx}$  скачком изменится до нового значения

$U_2$  и останется равным ему при дальнейшем росте e(t). При уменьшении e(t),  $U_{\delta_{\theta/X}}$  оудет оставаться неизменным до момента, когда управляющее напряжение достигнет второго порогового уровня  $\mathcal{E}_2$ , при котором  $U_{\delta_{\theta/X}}$  скачком перейдет в исходное состояние устойчивого равновесия. Ширина петли гистерезиса — напряжение  $\mathcal{E}_{\tau}$ , называемое напряжением гистерезиса, является во многих случаях важной характеристикой триггера.

Характеристики вида рис.4.І можно получить при использовании газоразрядных приборов (неоновых ламп, тиратронов), полупроводниковых приборов ( туннельных диодов, тиристоров) и электронных ламп в динатронном или транзитронном режимах.

Но наибольшее распространение получили триггеры, основанные на использовании усилителей ( транзисторных или ламповых), замкнутых в петлю положительной обратной связи с коэффициентом петлевого усиления  $K_o > 1$  .

Так как электронные ключи, рассмотренные в главе I, обладают определенным коэффициентом усиления, то они очень широко применяются для построения триггерных схем.